# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note : Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

## MITSUBISHI 16-BIT SINGLE-CHIP MICROCOMPUTER M16C FAMILY / M16C/60 SERIES

## http://www.infomicom.maec.co.jp/indexe.htm

Before using this material, please visit the above website to confirm that this is the most current document available.

#### -Keep safety first in your circuit designs!-

Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

#### -Notes regarding these materials-

- These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party.

- Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Mitsubishi Electric Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Mitsubishi Electric Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Mitsubishi Electric Corporation by various means, including the Mitsubishi Semiconductor home page (http://www.mitsubishichips.com).

- When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Mitsubishi Electric Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- Mitsubishi Electric Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semicon ductor product distributor for further details on these materials or the products con tained therein.

### How to Use This Manual

This user's manual is written for the M16C/62A group.

The reader of this manual is expected to have the basic knowledge of electric and logic circuits and microcomputers.

This manual explains a function of the following kind.

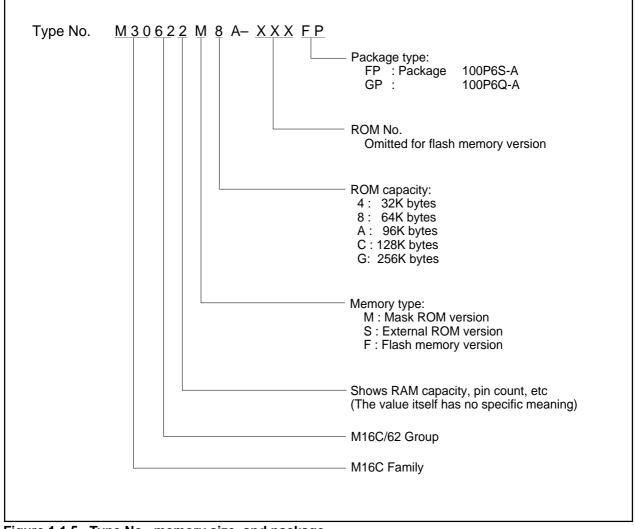

- M30620M8A-XXXFP/GP

- M30620MAA-XXXFP/GP

- M30622M4A-XXXFP/GP

- M30622M8A-XXXFP/GP

- M30622MCA-XXXFP/GP M30624MGA-XXXFP/GP

- M30622SAFP/GP

- M30620FCAFP/GP

- M30620MCA-XXXFP/GP

- M30622MAA-XXXFP/GP

- M30620SAFP/GP

- M30624FGAFP/GP

- M30620MCM-XXXFP/GP

- M30624MGM-XXXFP/GP

- M30620FCMFP/GP

• M30624FGMFP/GP

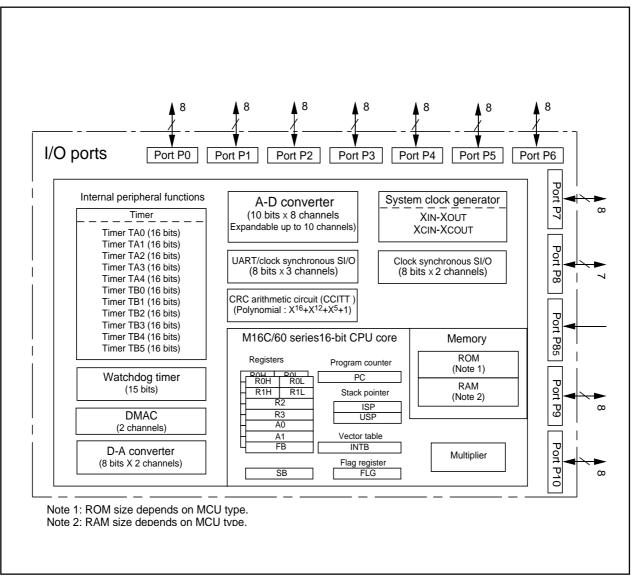

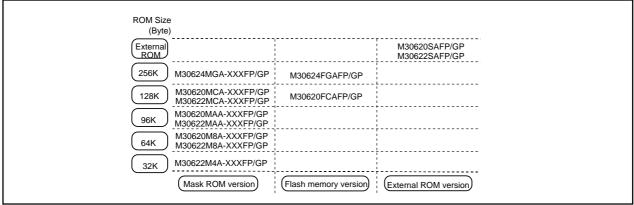

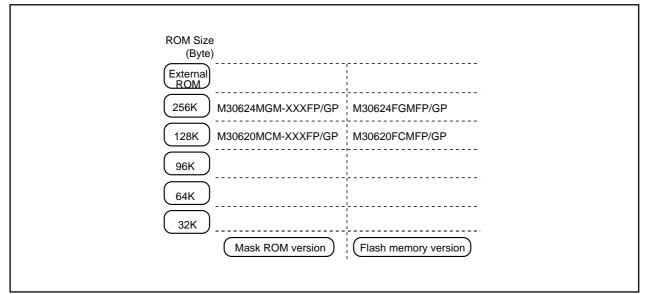

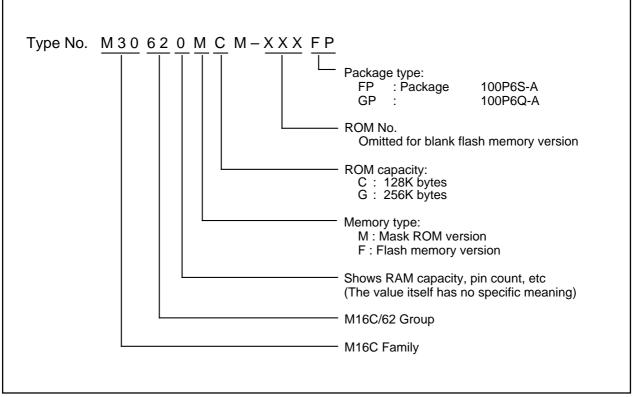

These products have similar features except for the memories, which differ from one product to another. This manual gives descriptions of M30622MCA-XXXFP. An electric characteristic refer to data sheet responded to. Memories built-in are as shown below. Be careful when writing a program, as the memories have different capacities.

| ROM Size<br>(Byte |                                          |                       |                                |

|-------------------|------------------------------------------|-----------------------|--------------------------------|

| External<br>ROM   | /                                        |                       | M30620SAFP/GP<br>M30622SAFP/GP |

| 256K              | M30624MGA-XXXFP/GP                       | M30624FGAFP/GP        |                                |

| (128K)            | M30620MCA-XXXFP/GP<br>M30622MCA-XXXFP/GP | M30620FCAFP/GP        |                                |

| 96K               | M30620MAA-XXXFP/GP<br>M30622MAA-XXXFP/GP |                       |                                |

| 64K               | M30620M8A-XXXFP/GP<br>M30622M8A-XXXFP/GP |                       |                                |

| 32K               | M30622M4A-XXXFP/GP                       |                       |                                |

|                   | Mask ROM version                         | Flash memory version  | External ROM version           |

| ROM Siz<br>(Byte  |                                          |                       |                                |

| External<br>ROM   | )                                        | ,<br>,<br>,<br>,<br>, |                                |

| 256K              | M30624MGM-XXXFP/GP                       | M30624FGMFP/GP        |                                |

| 128K              | M30620MCM-XXXFP/GP                       | M30620FCMFP/GP        |                                |

| 96K               | )                                        | -<br>-<br>-<br>-<br>- |                                |

| 64K               | )                                        | ,<br>,<br>,<br>,      |                                |

| 32K               | )                                        |                       |                                |

|                   | Mask ROM version                         | Flash memory version  |                                |

This manual comprises of five chapters. Use the suggested chapters as a reference for the following topics:

- \* To understand hardware specifications ...... Chapter 1 Hardware

- \* To understand the basic way of using peripheral features and the operation timing......Chapter 2 Peripheral Functions Usage

- \* To observe applications of peripheral features ...... Chapter 3 Examples of Peripheral Functions Applications

- \* To understand how to use external buses ...... Chapter 4 External Buses

- \* To know the difference between the mask ROM Version and external ROM Version...... Chapter 5 External ROM Version

This manual includes a quick reference immediately following the Table of Contents and Table of Contents Classified by Function, indicate the page of the topic to be pursued. An index is also described at the end of this manual.

\* To find a page describing a peripheral function ...... Table of Contents Classified by Function

\* To find a page describing a specific register by the register address...... Quick Reference to Pages Classified by Address

Extra application note explains follows, and please refer to each application note in addition to above.

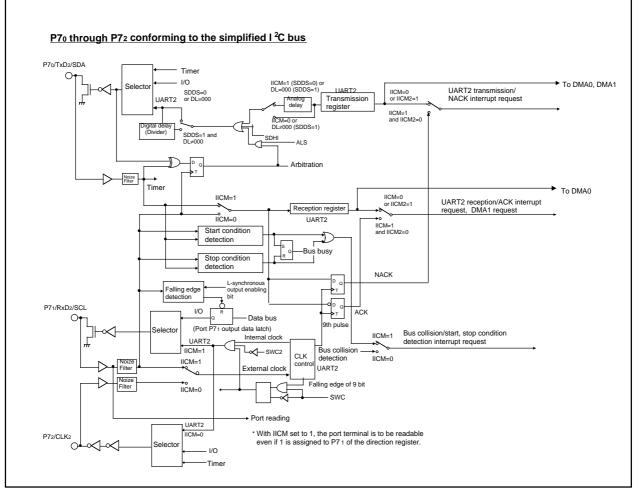

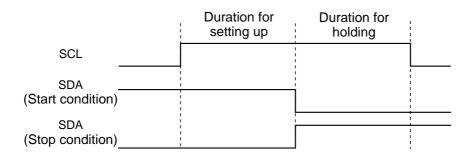

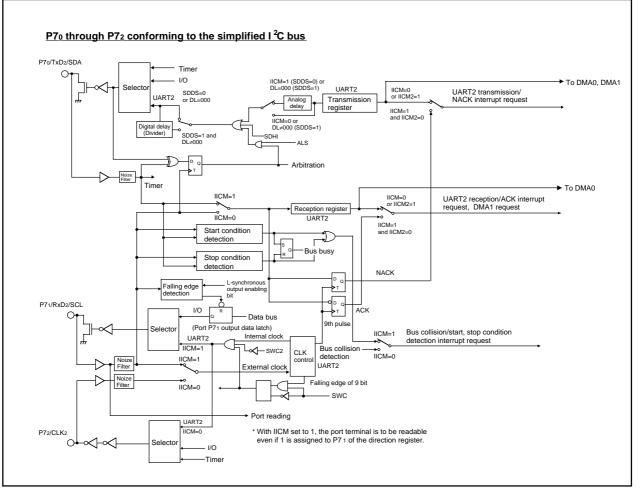

\* I<sup>2</sup>C BUS ...... M16C/62 Group SIMPLE I<sup>2</sup>C BUS

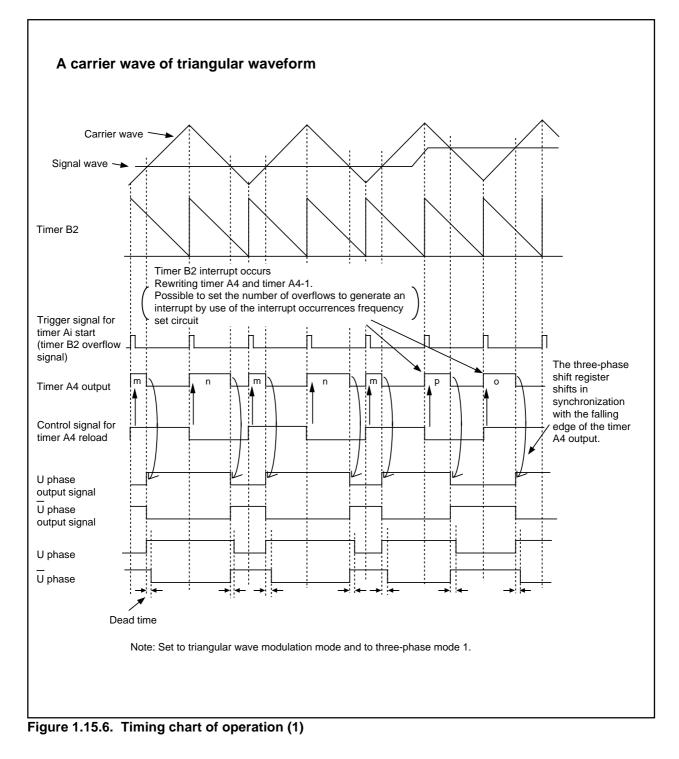

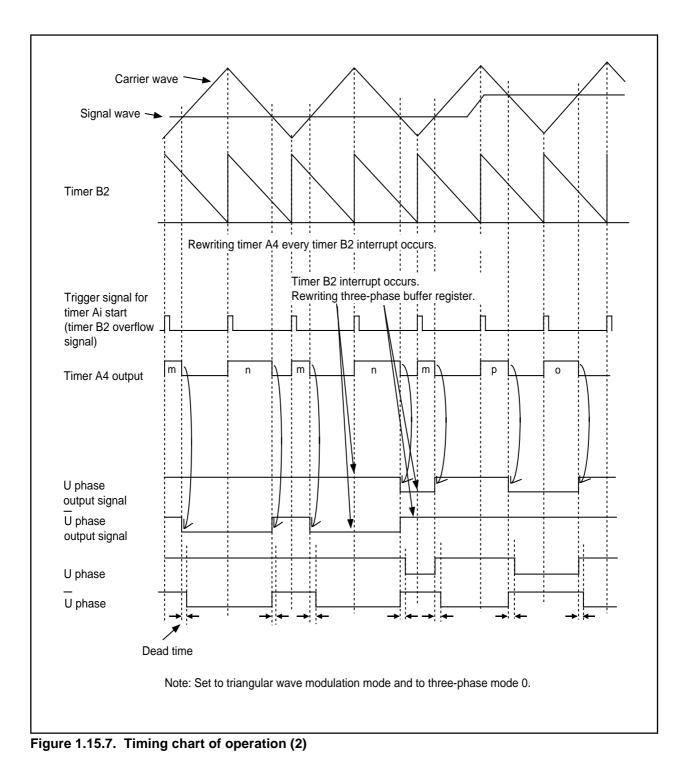

\* Three-phase motor control timer function ... M16C/62 Group THREE-PHASE MOTOR CONTROL

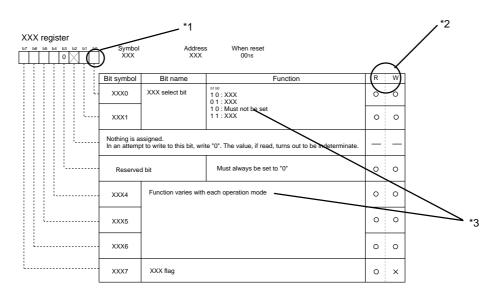

The figure of each register configuration describes its functions and attributes as follows :

\*1

Blank: Set to "0" or "1" according to intended use

- 0: Set to "0"

- 1: Set to "1"

- X: Nothing is assigned

\*2

#### R: Read

- O.....Possible to read

- X.....Impossible to read

- -....Nothing is assigned

- W: Write

- O.....Possible to write

- X.....Written value is invalid

- When write, value can be "0" or "1"

- -....Nothing is assigned

#### \*3

Terms to use here are explained as follows.

Nothing is assigned

Nothing is assigned to the bit concerned. When write, set "0" for new function in future plan.

• Must not be set

Not select. The operation at having selected is not guaranteed.

Reserved bit

Reserved bit. Set the specified value.

• Function varies with each operation mode

Bit function changes according to the mode of peripheral functions.

Invalid in A mode

The bit concerned has no function in A mode. Set the specified value.

• Valid when bit A="0"

When bit A is "1", the bit concerned has no function. When bit A is "0", the bit concerned has function.

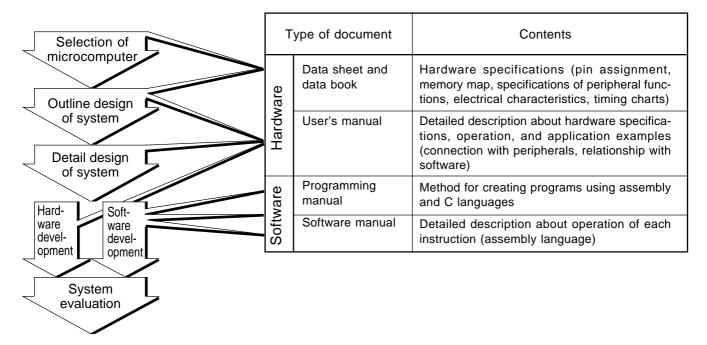

### M16C Family-related document list

#### Usages

#### (Microcomputer development flow)

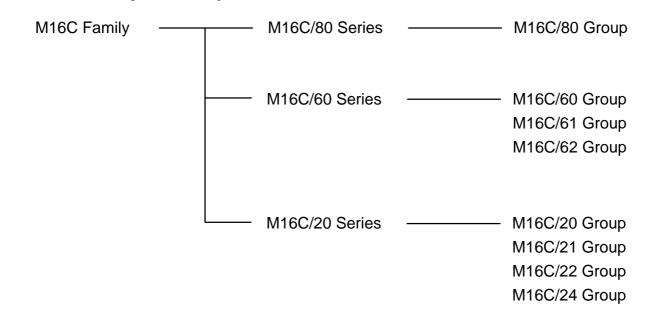

### M16C Family Line-up

## Table of Contents

## Chapter 1 Hardware \_\_\_\_\_

| Description 1-                                      | -2 |

|-----------------------------------------------------|----|

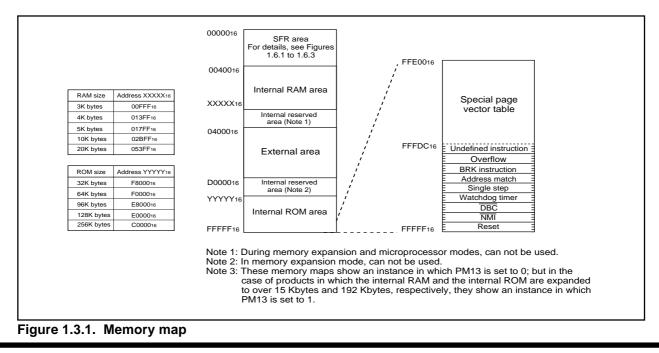

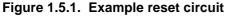

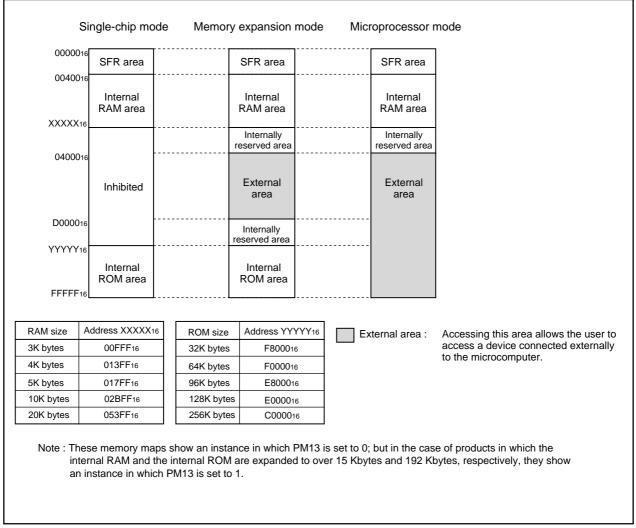

| Memory 1-1                                          | 11 |

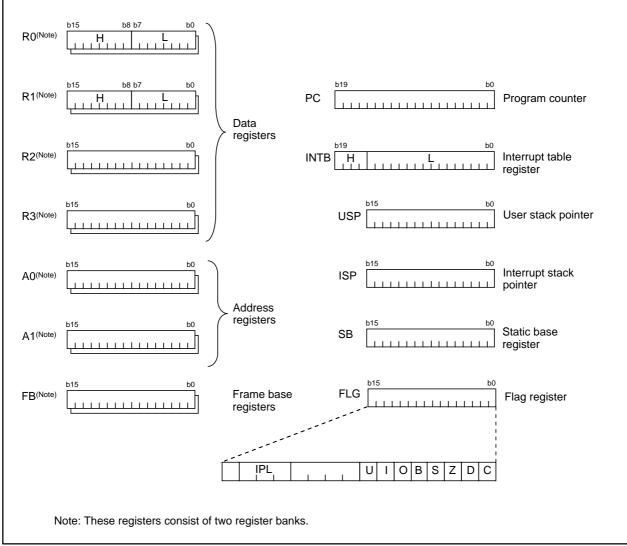

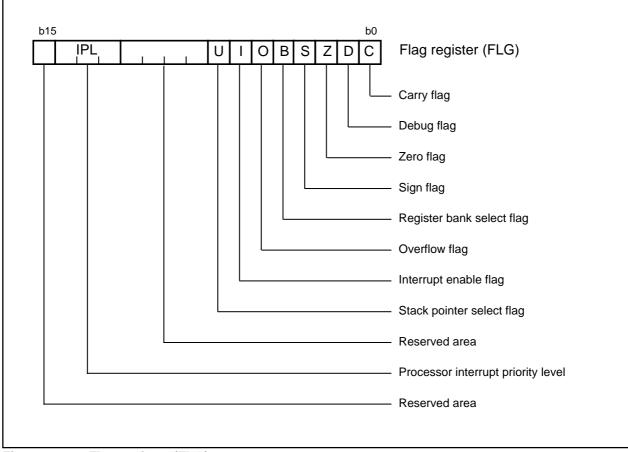

| Central Processing Unit (CPU) 1-1                   | 12 |

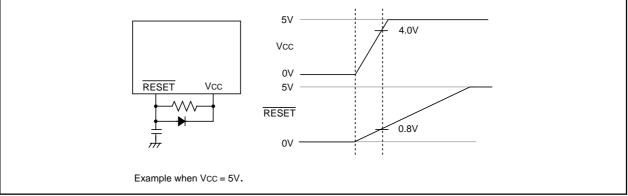

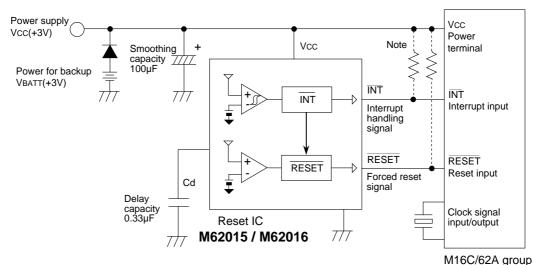

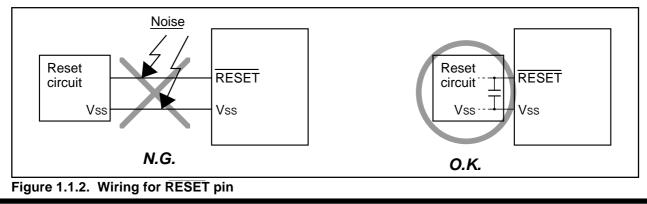

| Reset 1-1                                           | 15 |

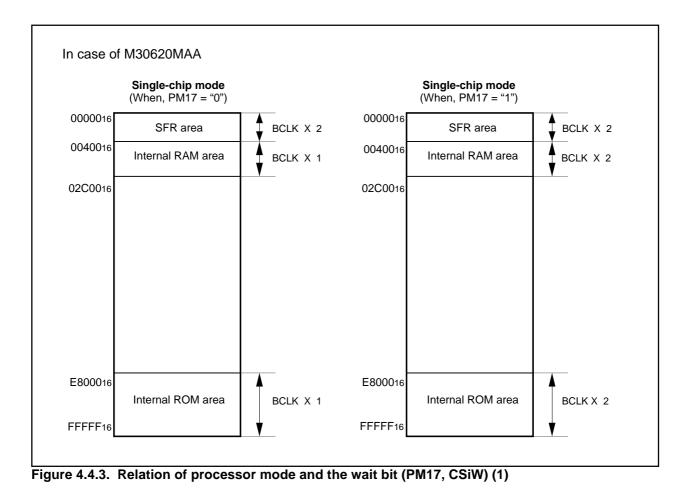

| Processor Mode 1-2                                  | 22 |

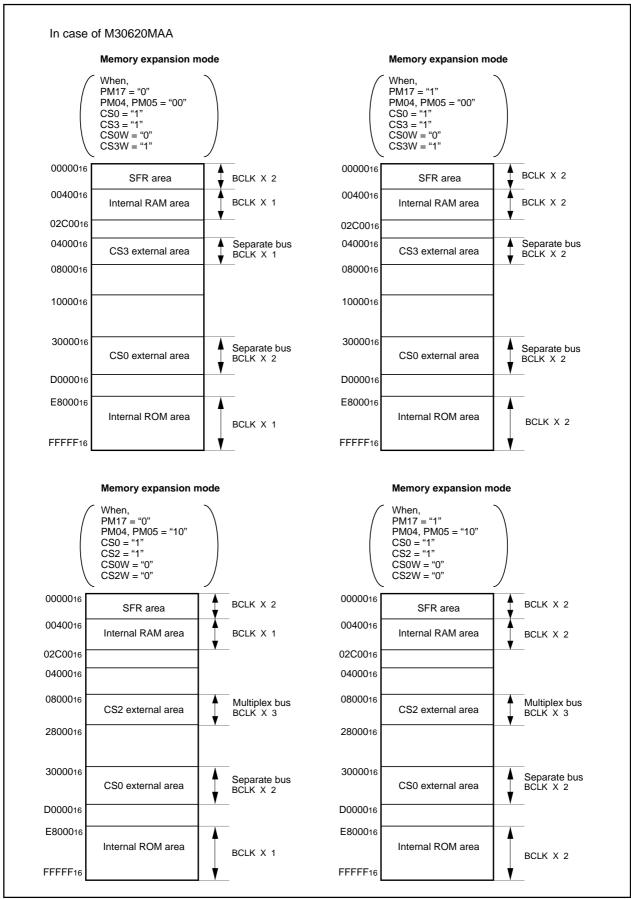

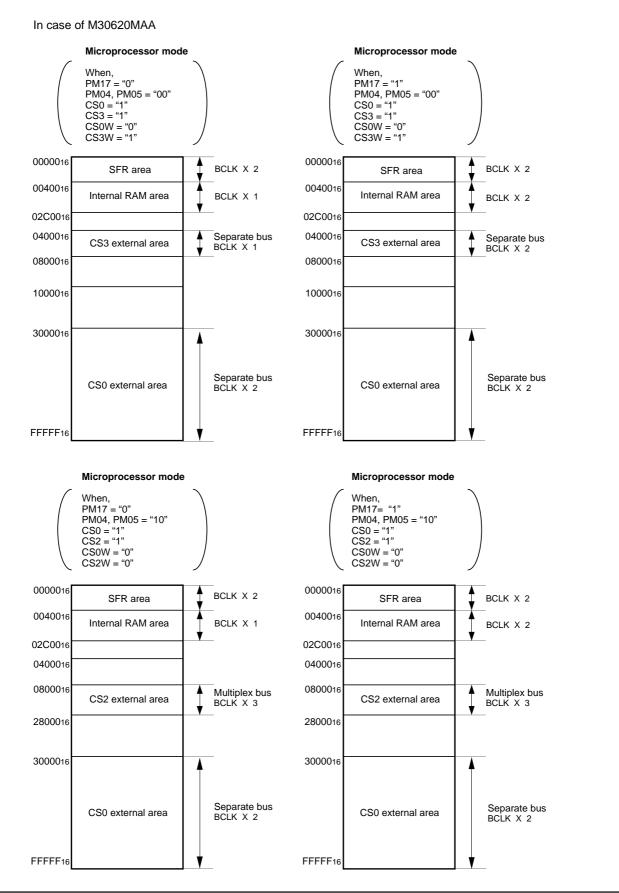

| Bus Settings 1-2                                    | 26 |

| Bus Control 1-2                                     | 28 |

| Clock Generating Circuit 1-3                        | 36 |

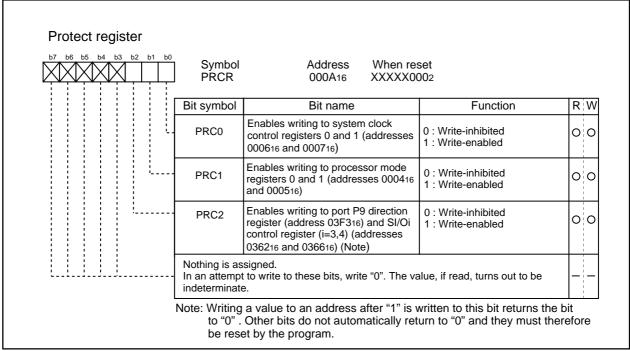

| Protection 1-4                                      | 45 |

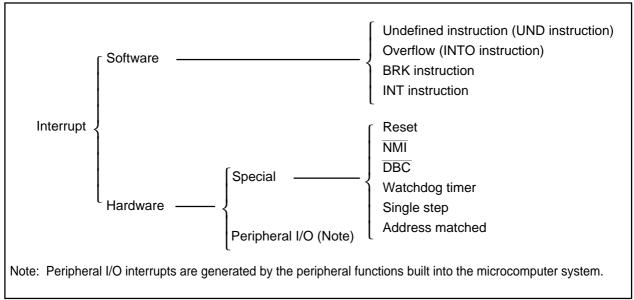

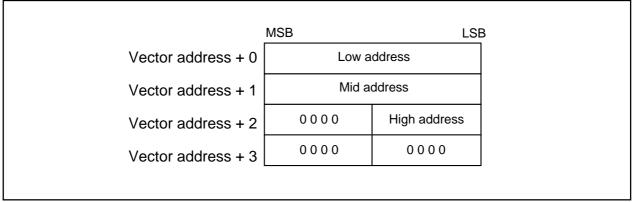

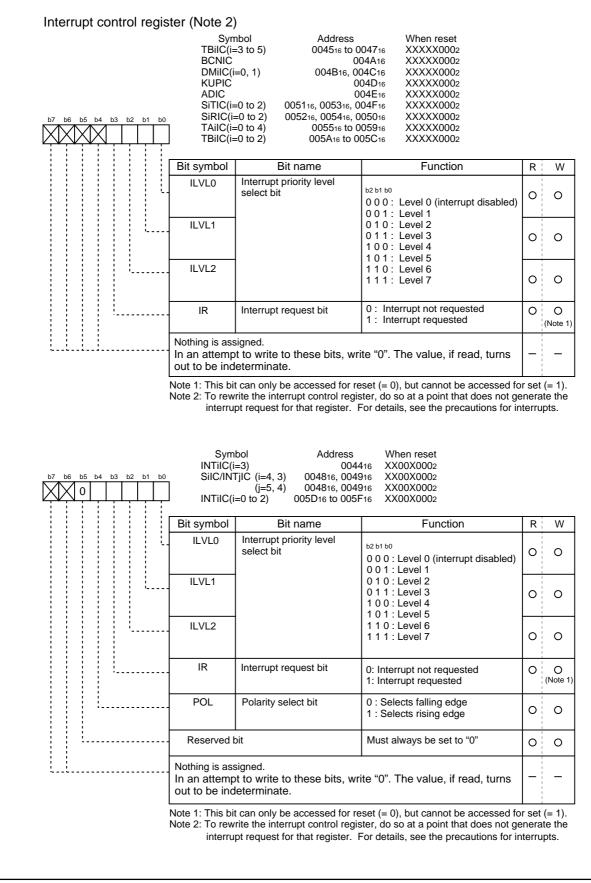

| Overview of Interrupt 1-4                           | 46 |

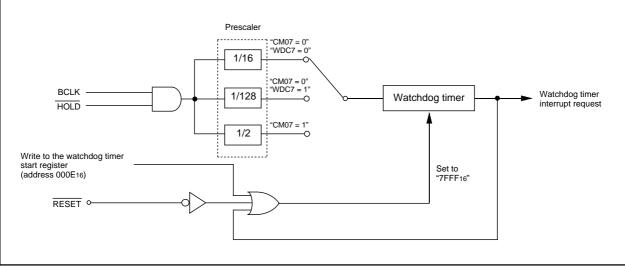

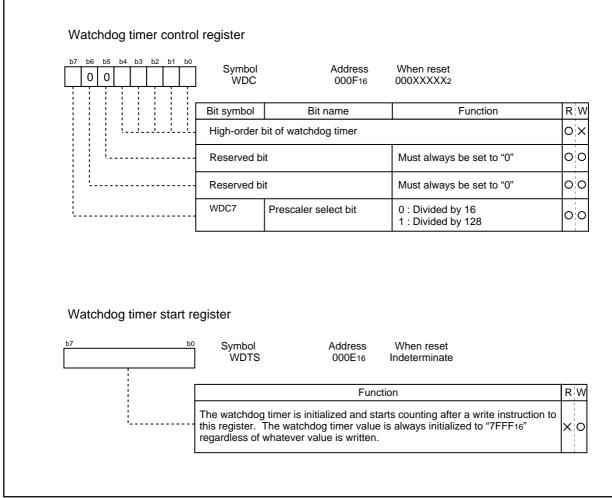

| Watchdog Timer 1-6                                  | 66 |

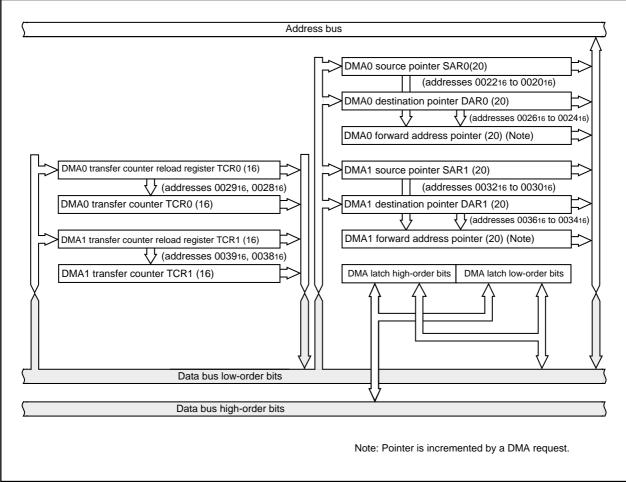

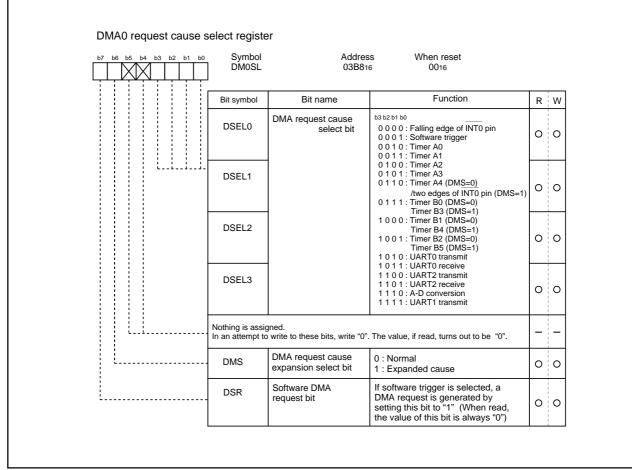

| DMAC 1-6                                            | 68 |

| Timer 1-7                                           | 78 |

| Timer A                                             | 80 |

| Timer B 1-9                                         | 90 |

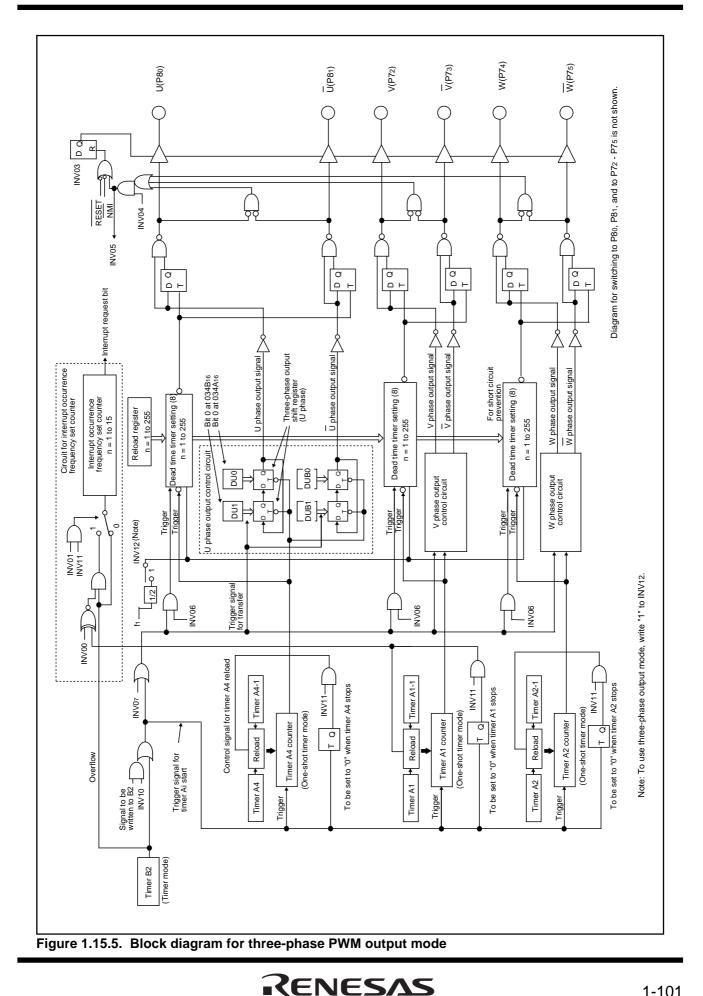

| Timers' functions for three-phase motor control 1-9 | 96 |

| Serial I/O 1-10                                     | 08 |

| A-D Converter 1-14                                  | 49 |

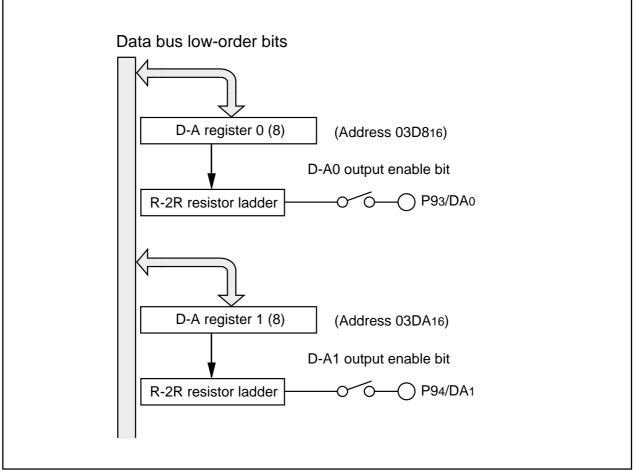

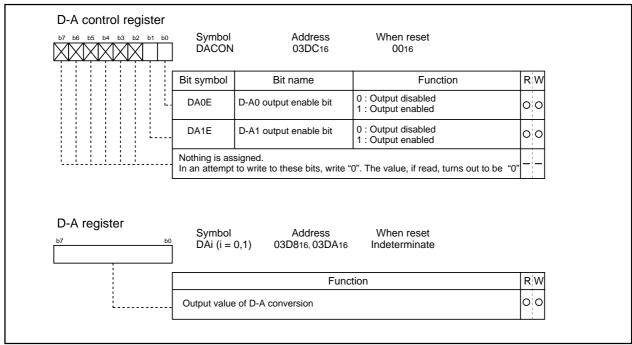

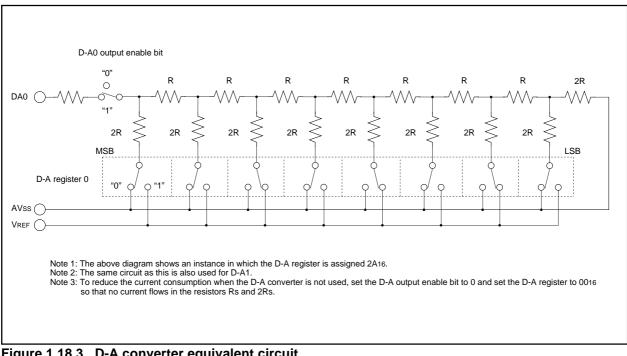

| D-A Converter 1-15                                  | 59 |

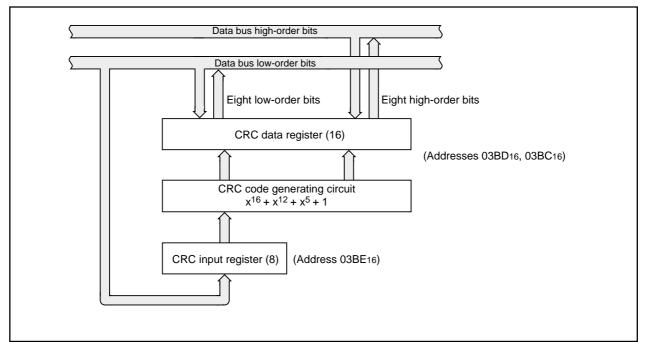

| CRC Calculation Circuit 1-16                        | 61 |

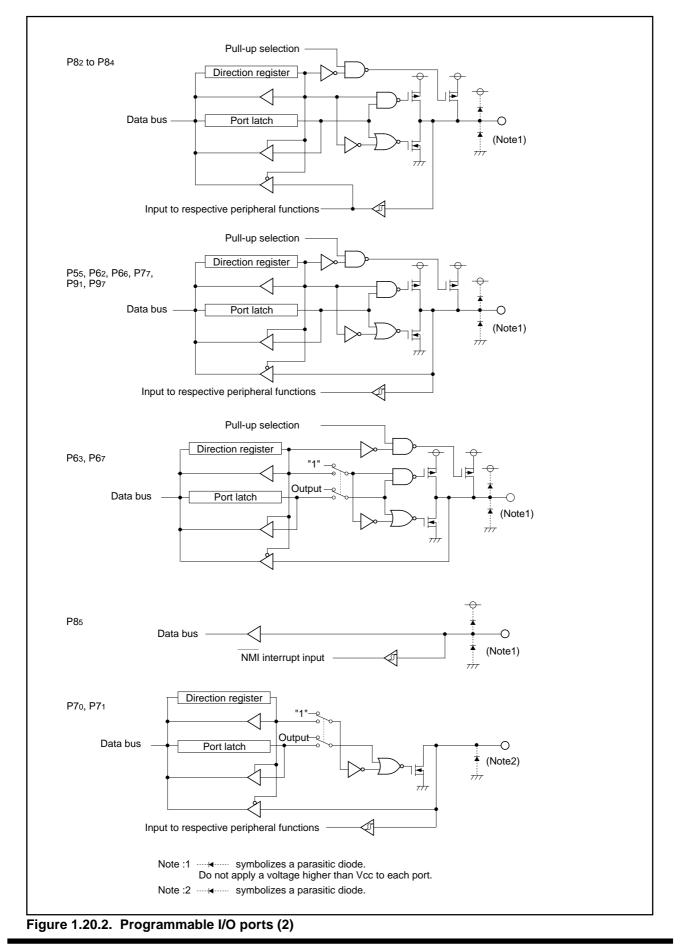

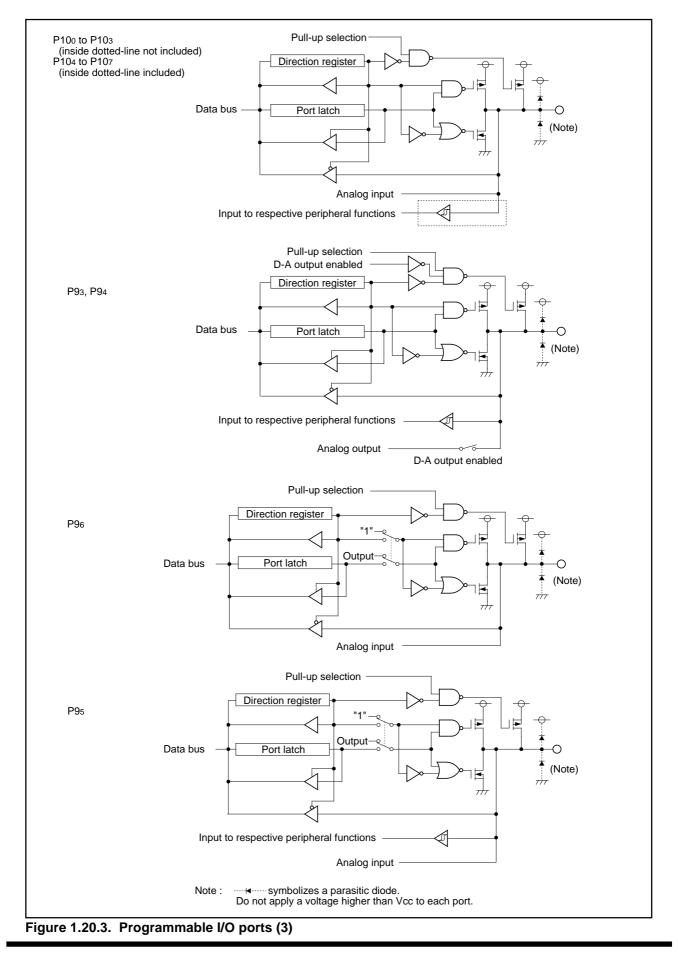

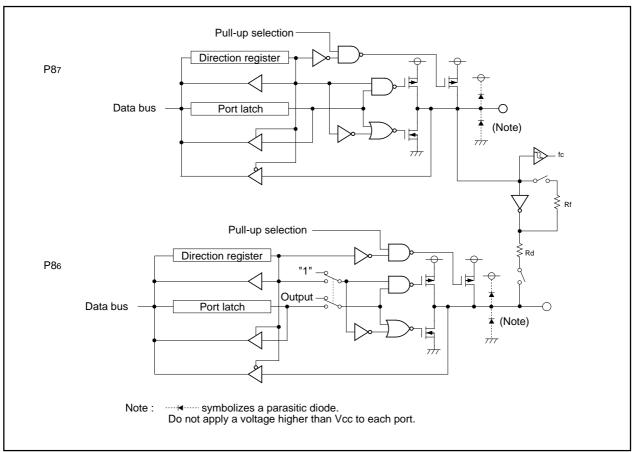

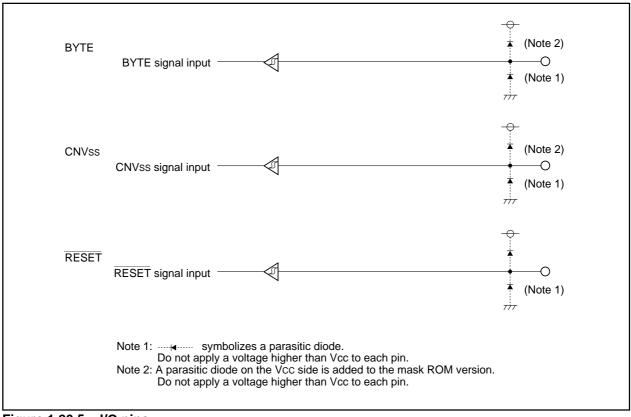

| Programmable I/O Ports 1-16                         | 63 |

| Flash Memory Version 1-21                           | 17 |

|                                                     |    |

### Chapter 2 Peripheral Functions Usage \_\_\_\_\_

| 2.1 Protect Usage 2                        | 2-2         |

|--------------------------------------------|-------------|

| 2.1.1 Overview of the protect usage 2      | 2-2         |

| 2.1.2 Protect Operation                    | <u>2</u> -4 |

| 2.1.3 Precaution for Protect 2             | 2-5         |

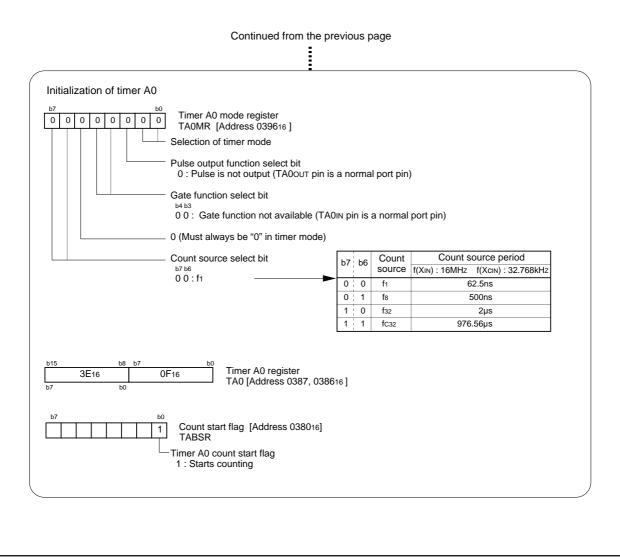

| 2.2 Timer A Usage 2                        | 2-6         |

| 2.2.1 Overview of the timer A usage 2      | 2-6         |

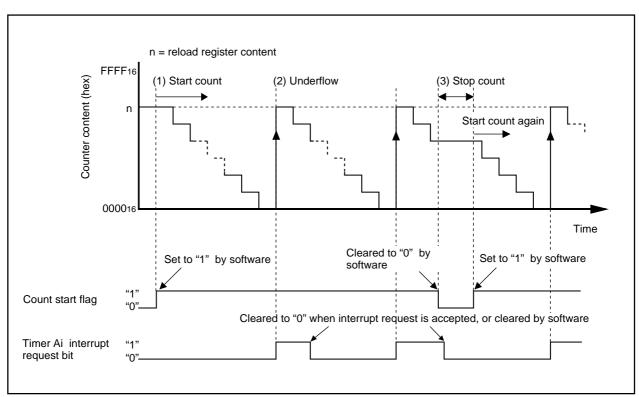

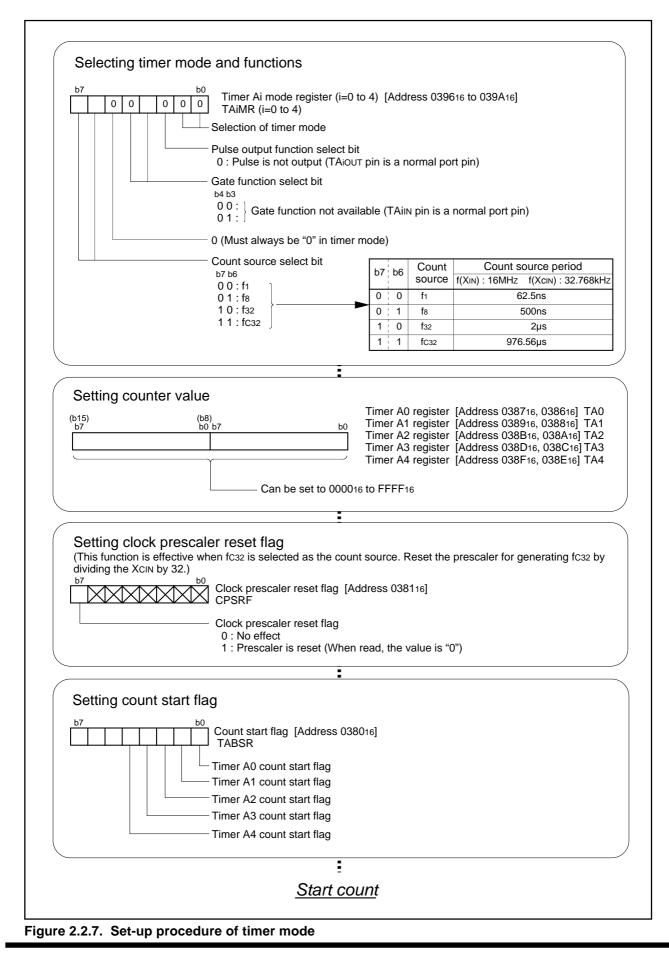

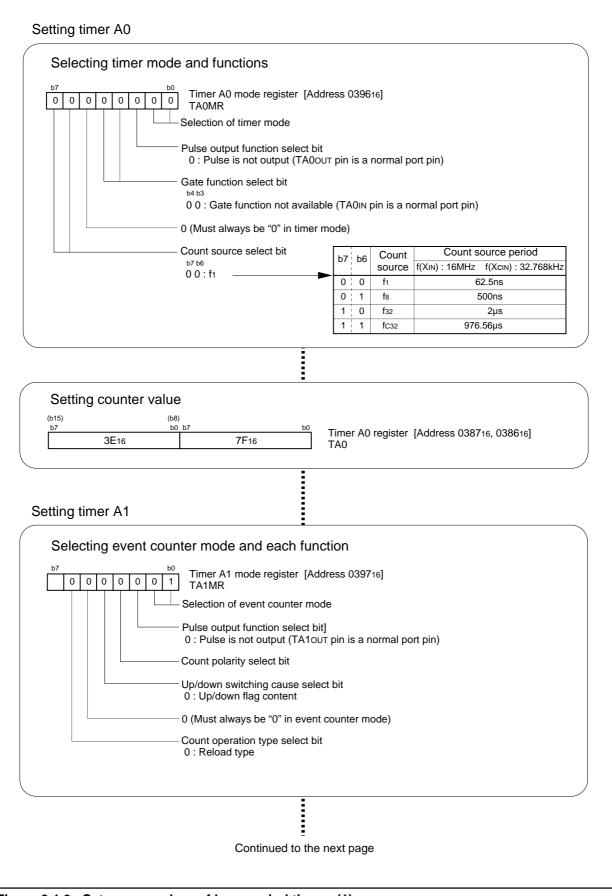

| 2.2.2 Operation of Timer A (timer mode) 2- | 12          |

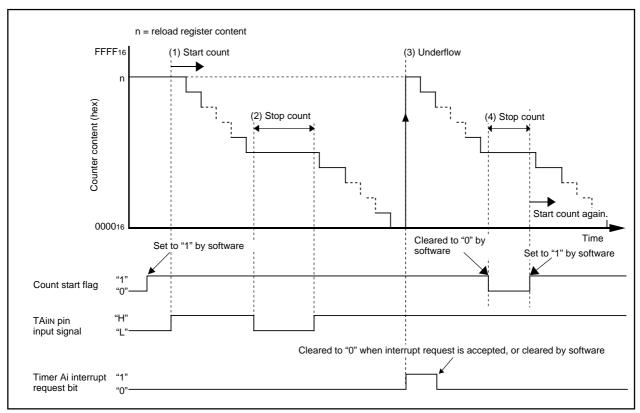

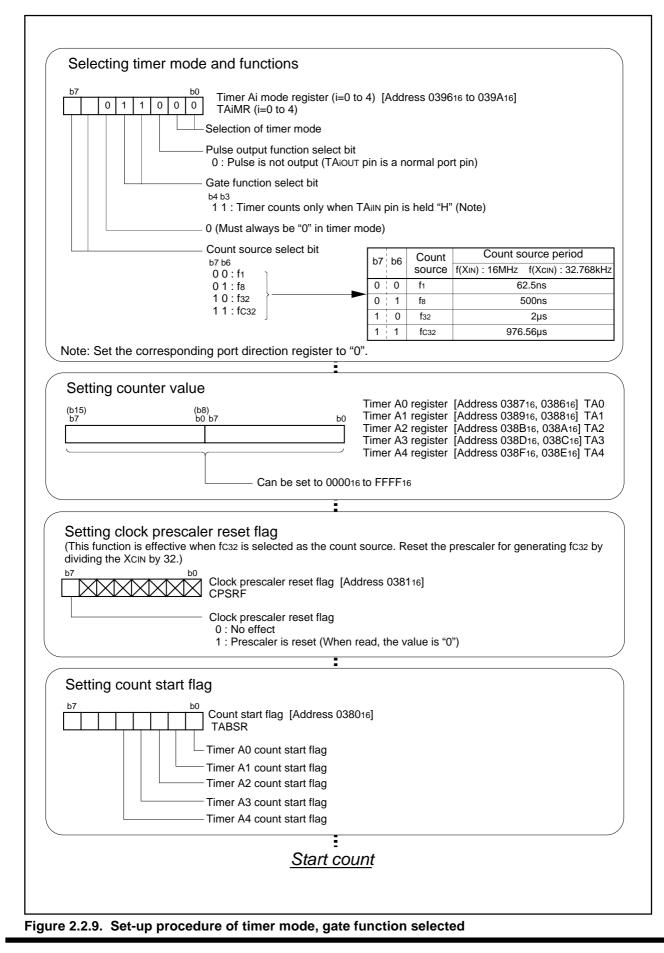

| 2.2.3 Operation of Timer A (timer mode, gate function selected)                                                                            | 2-14 |

|--------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.2.4 Operation of Timer A (timer mode, pulse output function selected)                                                                    | 2-16 |

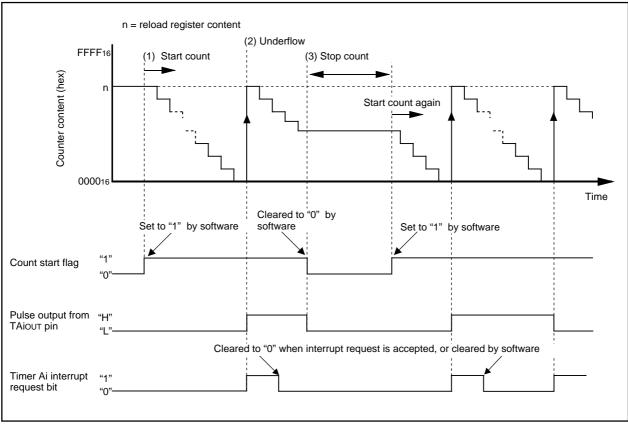

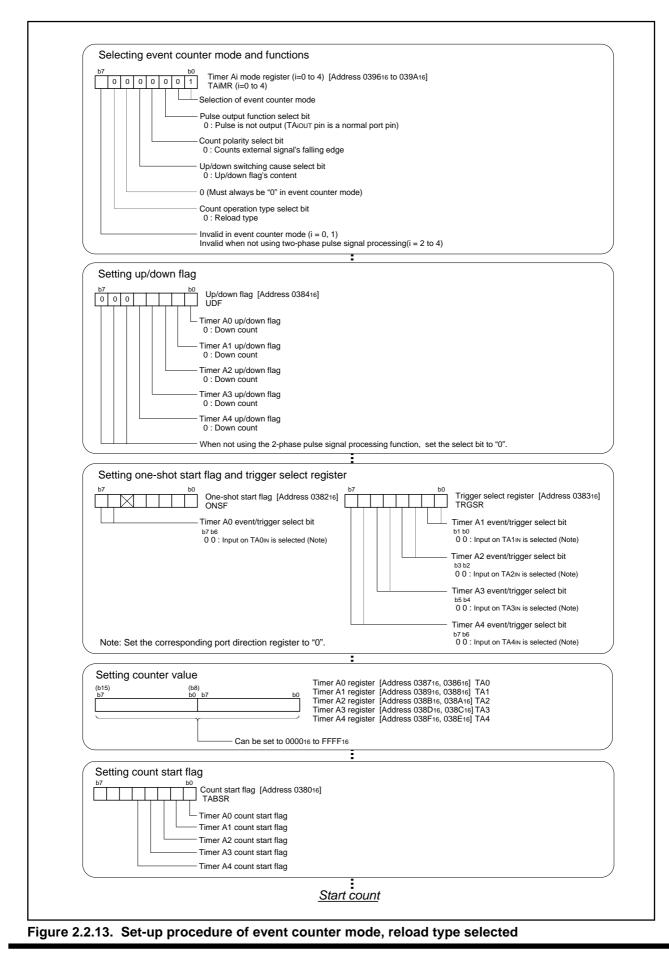

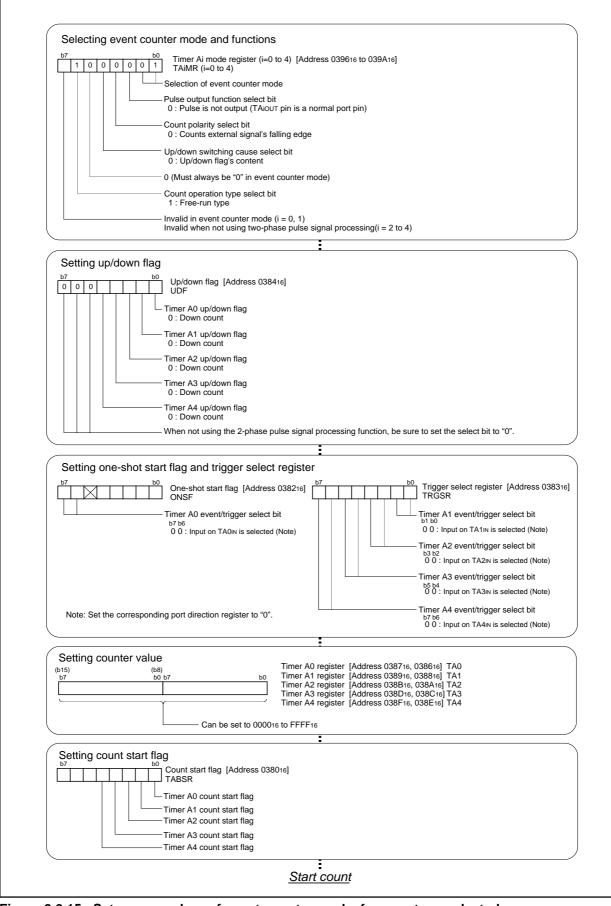

| 2.2.5 Operation of Timer A (event counter mode, reload type selected)                                                                      | 2-18 |

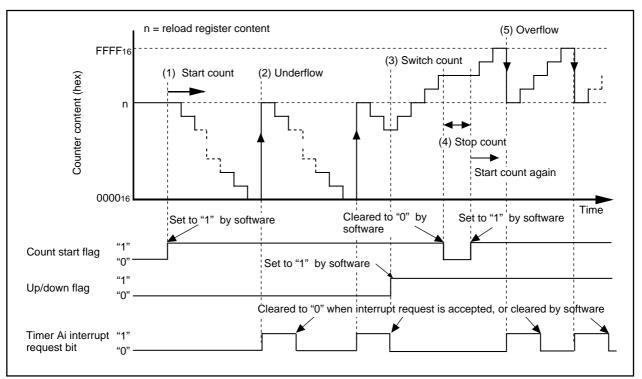

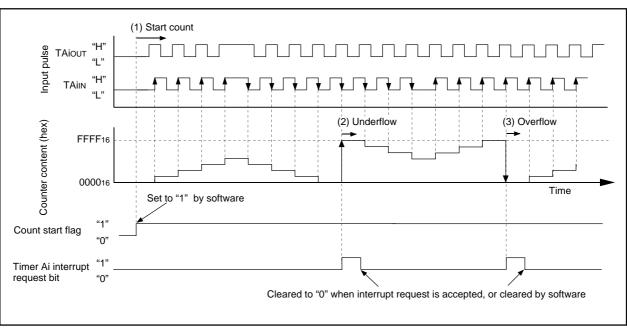

| 2.2.6 Operation of Timer A (event counter mode, free run type selected)                                                                    | 2-20 |

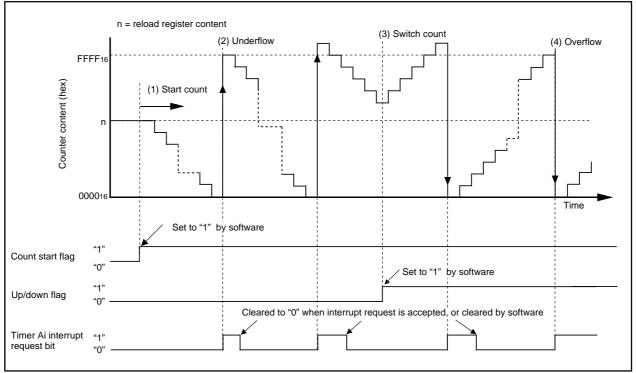

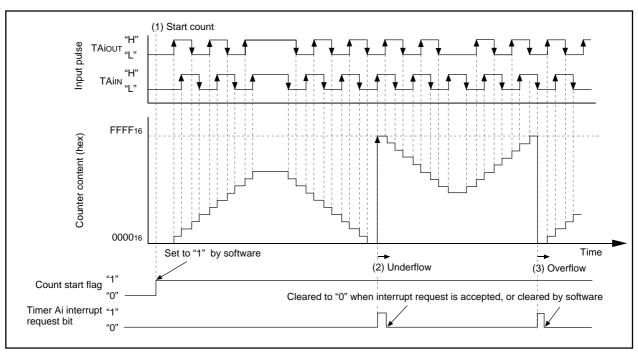

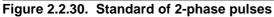

| 2.2.7 Operation of timer A (2-phase pulse signal process in event counter mode, normal mo<br>lected)                                       |      |

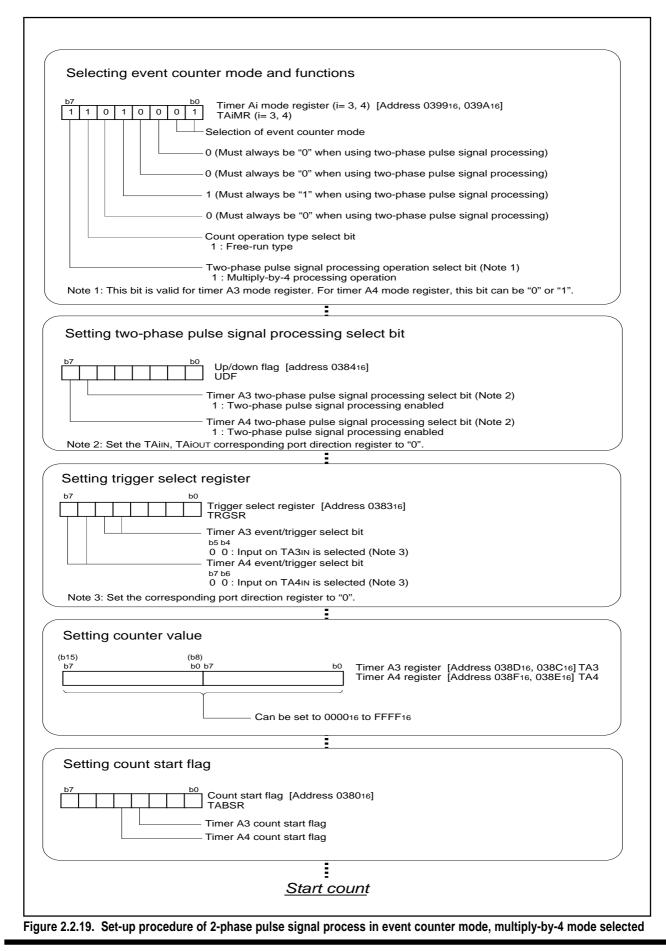

| 2.2.8 Operation of timer A (2-phase pulse signal process in event counter mode, multiply-by-<br>selected)                                  |      |

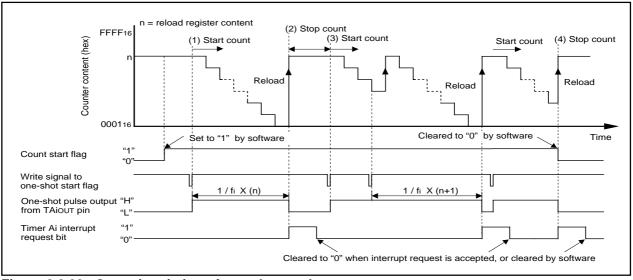

| 2.2.9 Operation of Timer A (one-shot timer mode)                                                                                           | 2-26 |

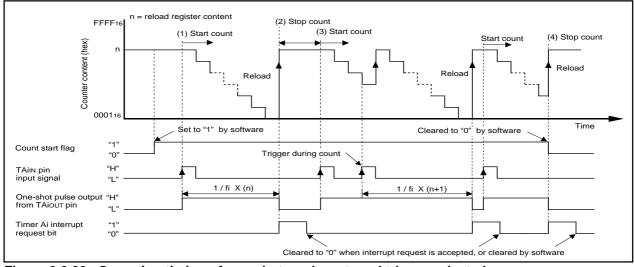

| 2.2.10 Operation of Timer A (one-shot timer mode, external trigger selected)                                                               | 2-28 |

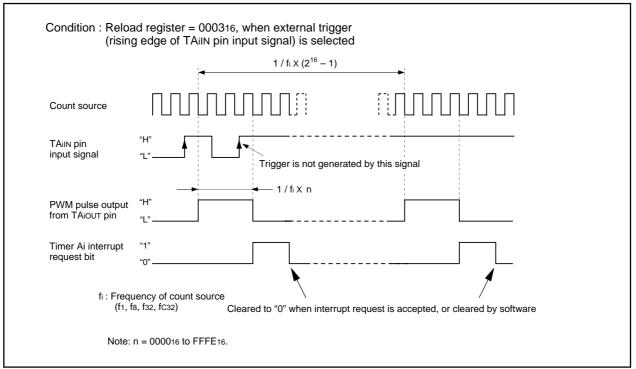

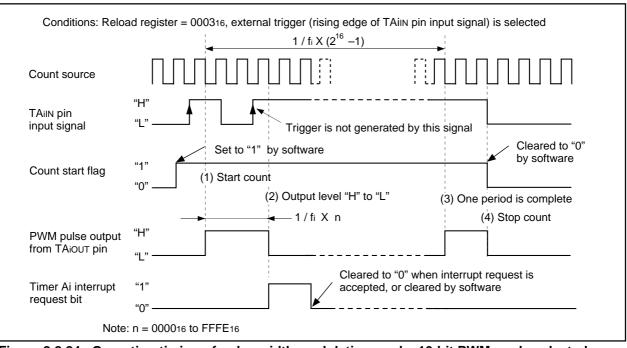

| 2.2.11 Operation of Timer A (pulse width modulation mode, 16-bit PWM mode selected)                                                        | 2-30 |

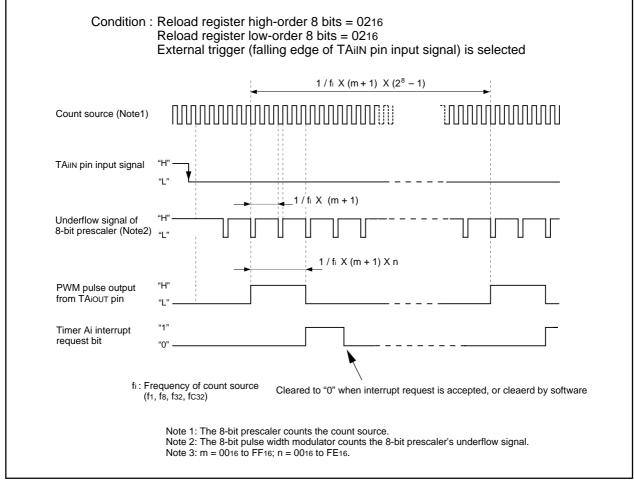

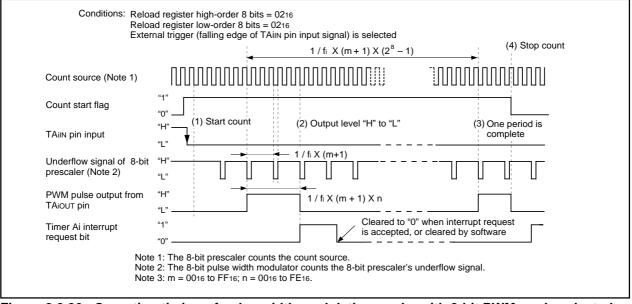

| 2.2.12 Operation of Timer A (pulse width modulation mode, 8-bit PWM mode selected)                                                         | 2-32 |

| 2.2.13 Precautions for Timer A (timer mode)                                                                                                | 2-34 |

| 2.2.14 Precautions for Timer A (event counter mode)                                                                                        | 2-35 |

| 2.2.15 Precautions for Timer A (one-shot timer mode)                                                                                       | 2-36 |

| 2.2.16 Precautions for Timer A (pulse width modulation mode)                                                                               | 2-37 |

| 2.3 Timer B Usage                                                                                                                          | 2-38 |

| 2.3.1 Overview of the timer B usage                                                                                                        | 2-38 |

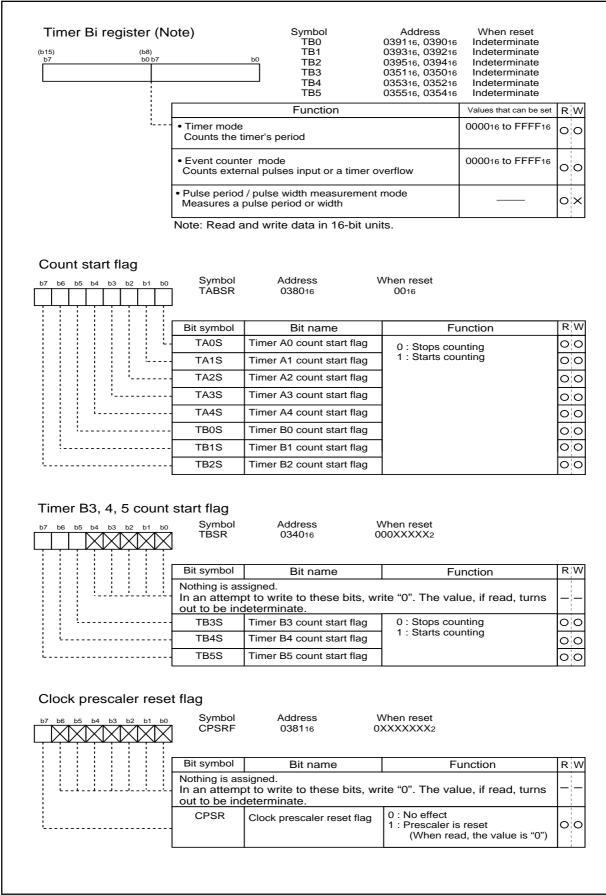

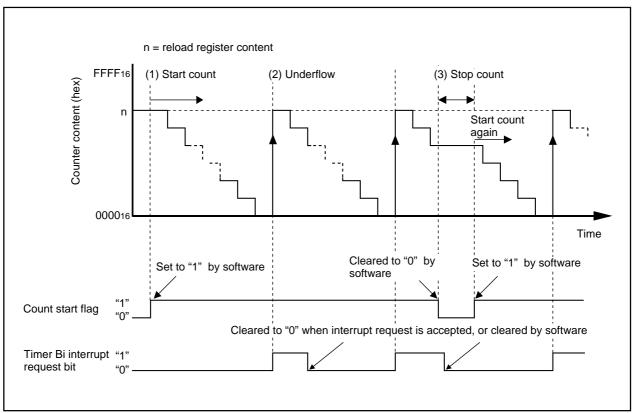

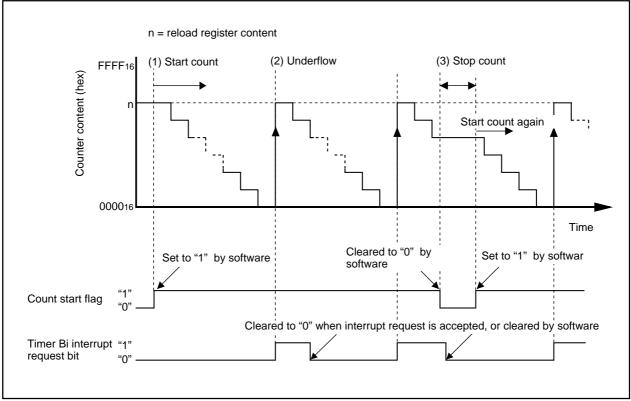

| 2.3.2 Operation of Timer B (timer mode)                                                                                                    | 2-42 |

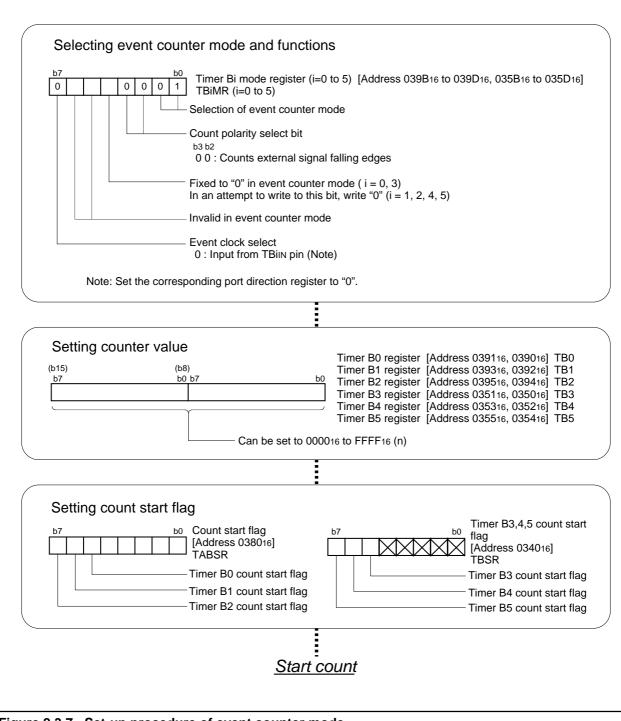

| 2.3.3 Operation of Timer B (event counter mode)                                                                                            | 2-44 |

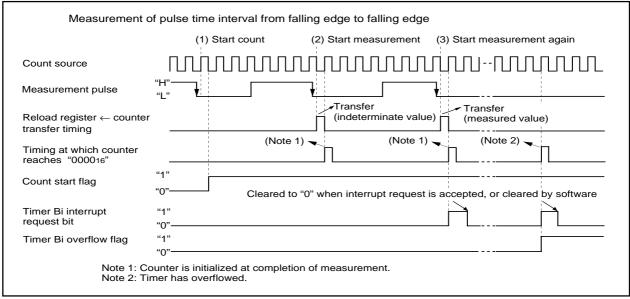

| 2.3.4 Operation of Timer B (pulse period measurement mode)                                                                                 | 2-46 |

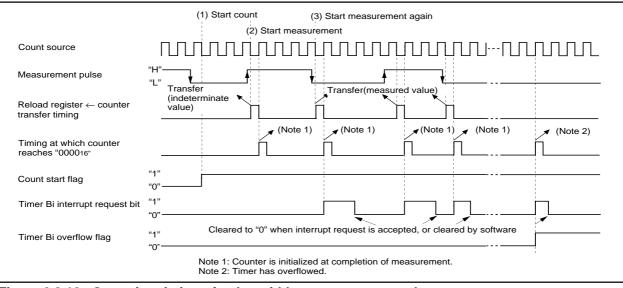

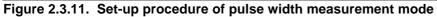

| 2.3.5 Operation of Timer B (pulse width measurement mode)                                                                                  | 2-48 |

| 2.3.6 Precautions for Timer B (timer mode, event counter mode)                                                                             | 2-50 |

| 2.3.7 Precautions for Timer B (pulse period/pulse width measurement mode)                                                                  | 2-51 |

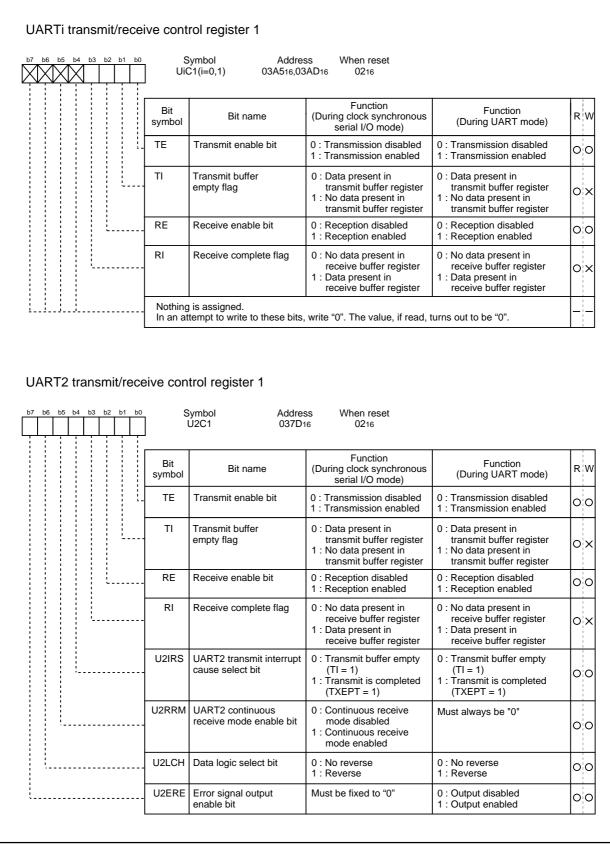

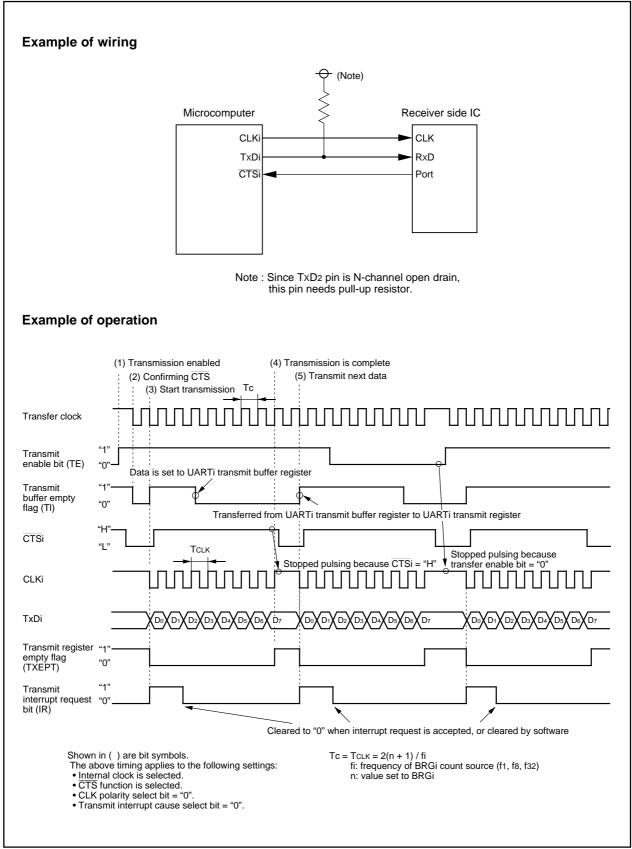

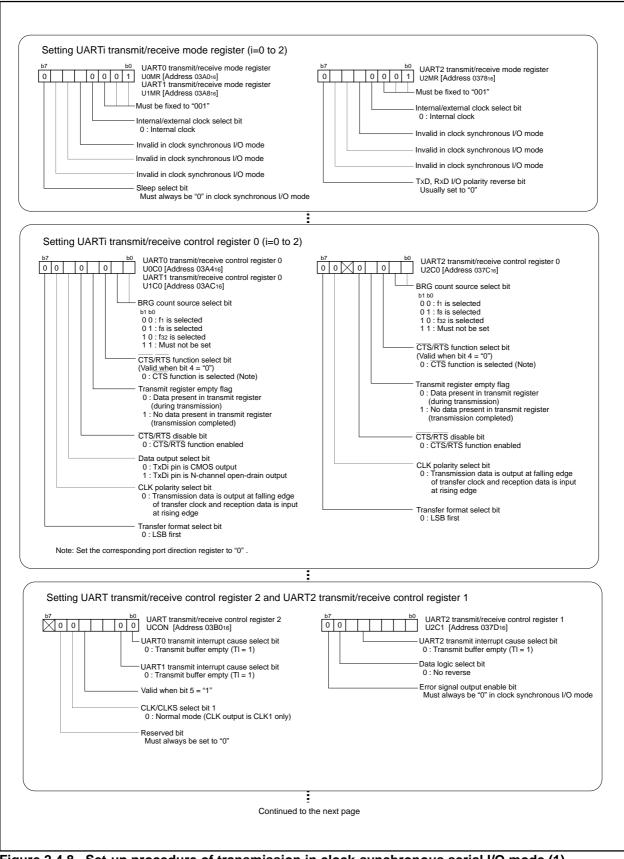

| 2.4 Clock-Synchronous Serial I/O Usage                                                                                                     | 2-52 |

| 2.4.1 Overview of the clock-synchronous serial I/O usage                                                                                   | 2-52 |

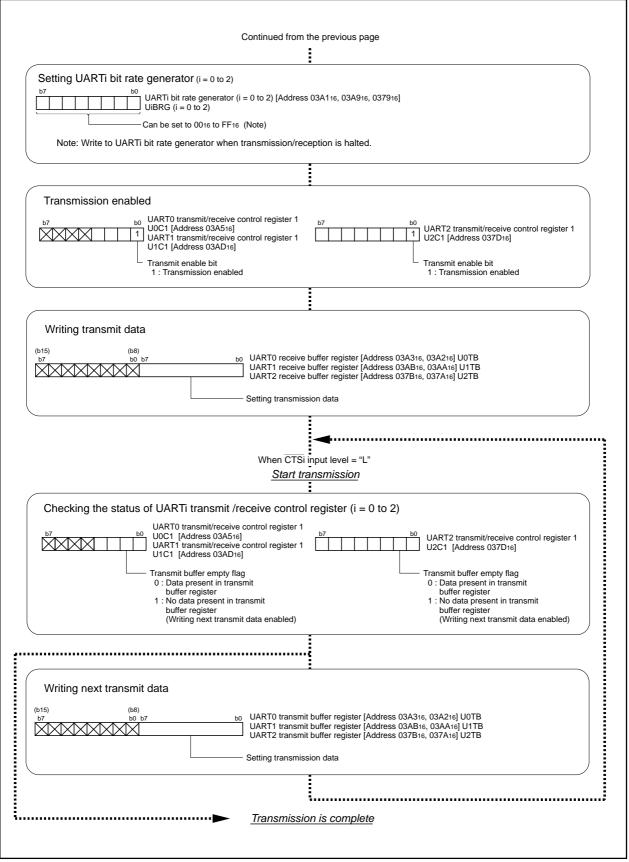

| 2.4.2 Operation of Serial I/O (transmission in clock-synchronous serial I/O mode)                                                          | 2-60 |

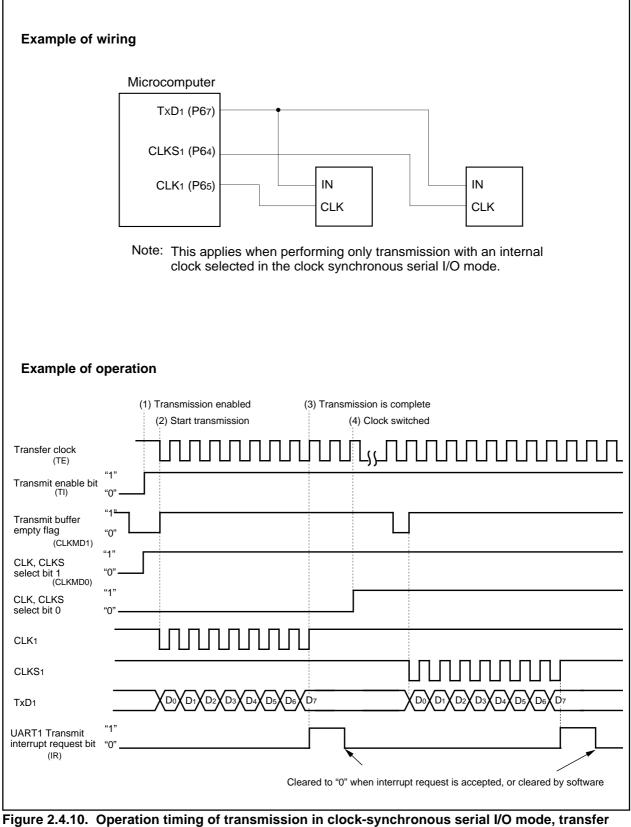

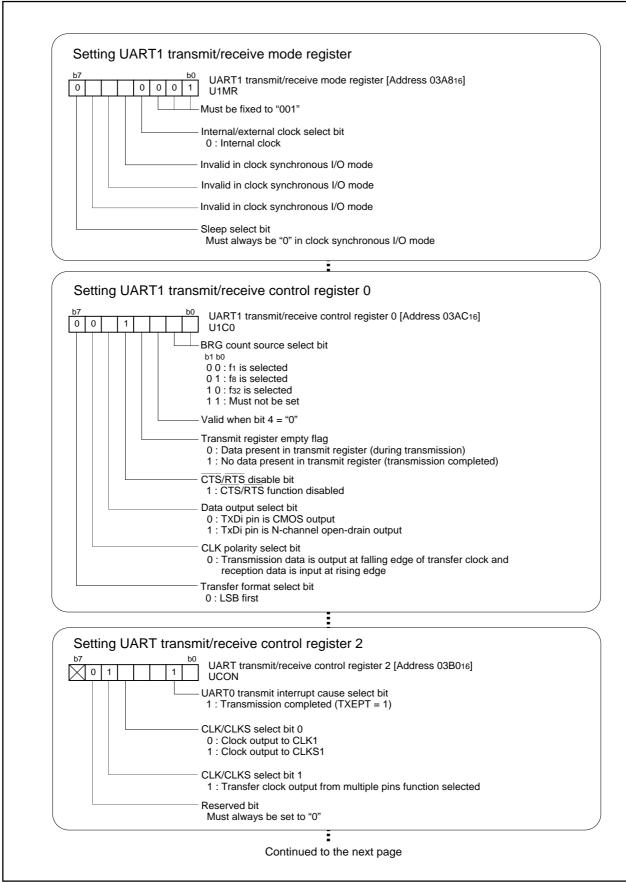

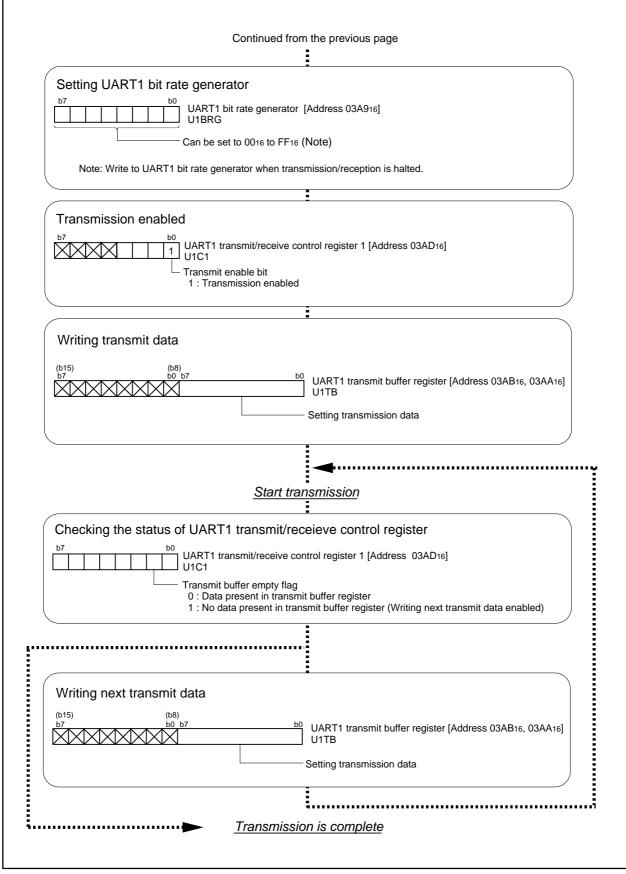

| 2.4.3 Operation of the Serial I/O (transmission in clock-synchronous serial I/O mode, transfe output from multiple pins function selected) |      |

| 2.4.4 Operation of Serial I/O (reception in clock-synchronous serial I/O mode)                                                             | 2-68 |

| 2.4.5 Precautions for Serial I/O (in clock-synchronous serial I/O)                                                                         | 2-72 |

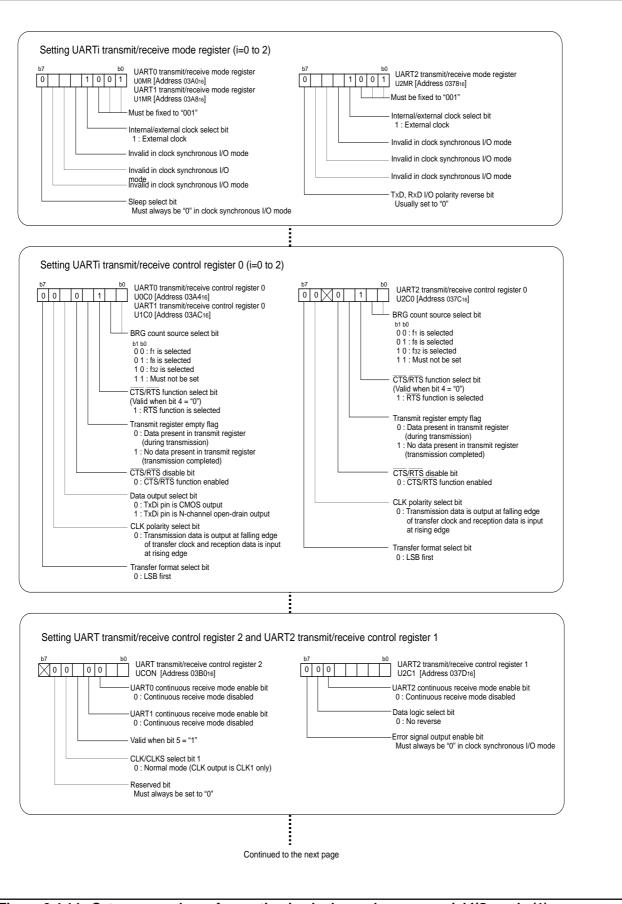

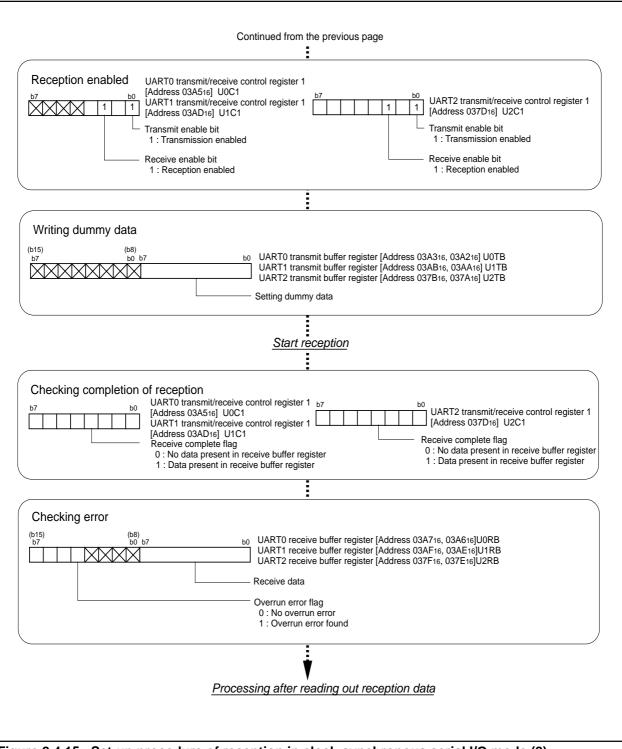

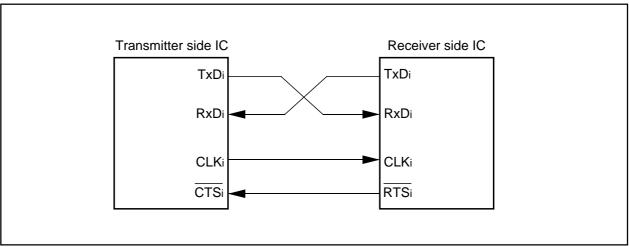

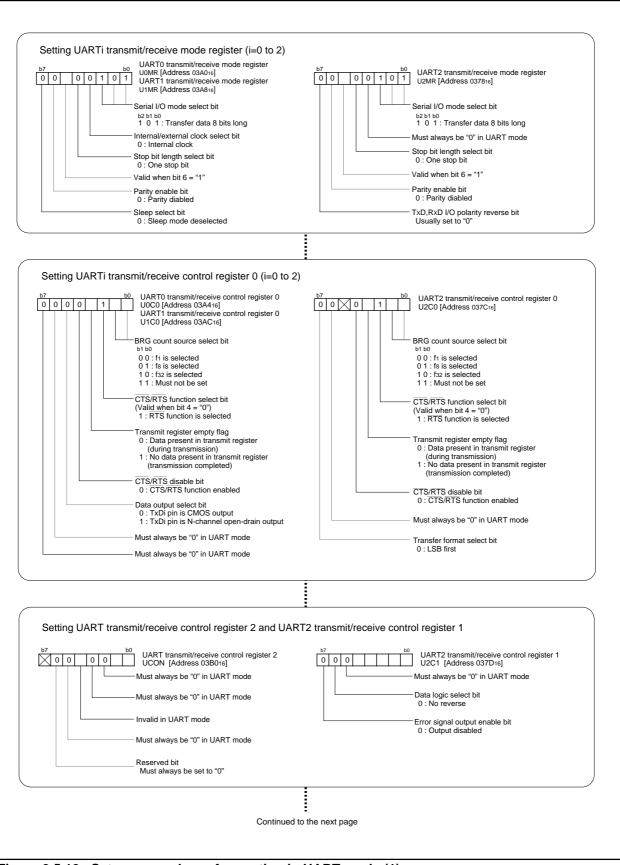

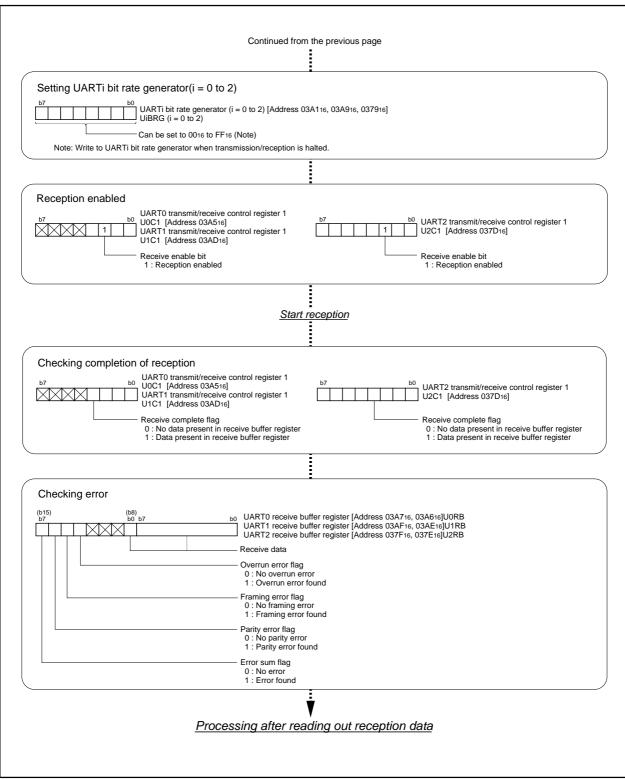

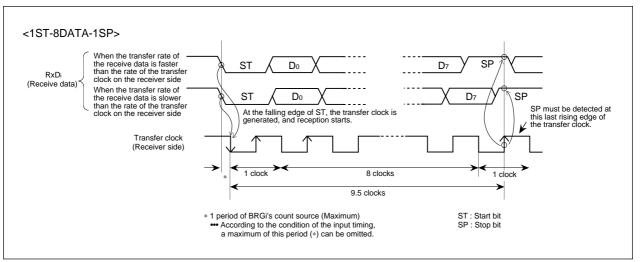

| 2.5 Clock-Asynchronous Serial I/O (UART) Usage                                                                                             | 2-74 |

| 2.5.1 Overview of the clock-asynchronous serial I/O usage                                                                                  | 2-74 |

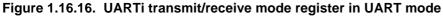

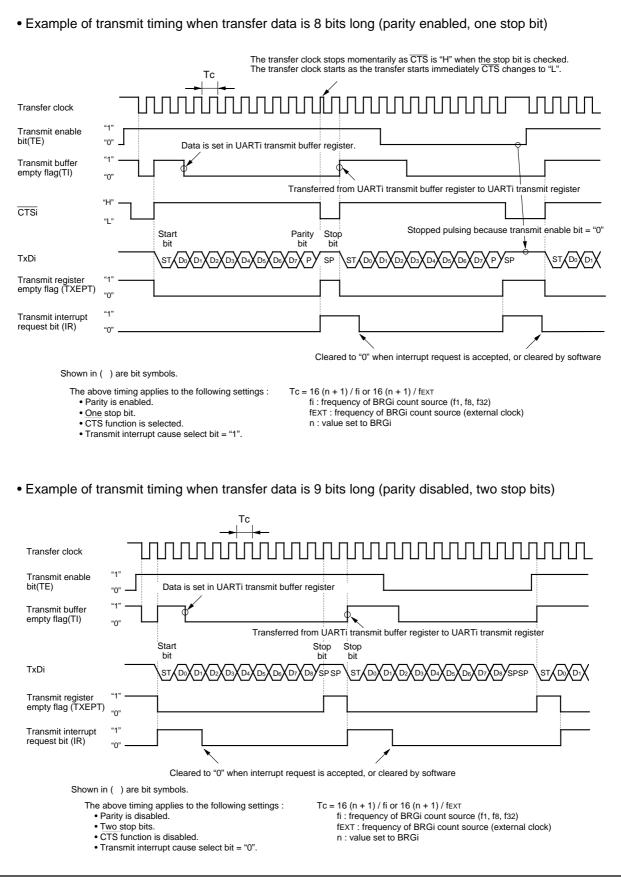

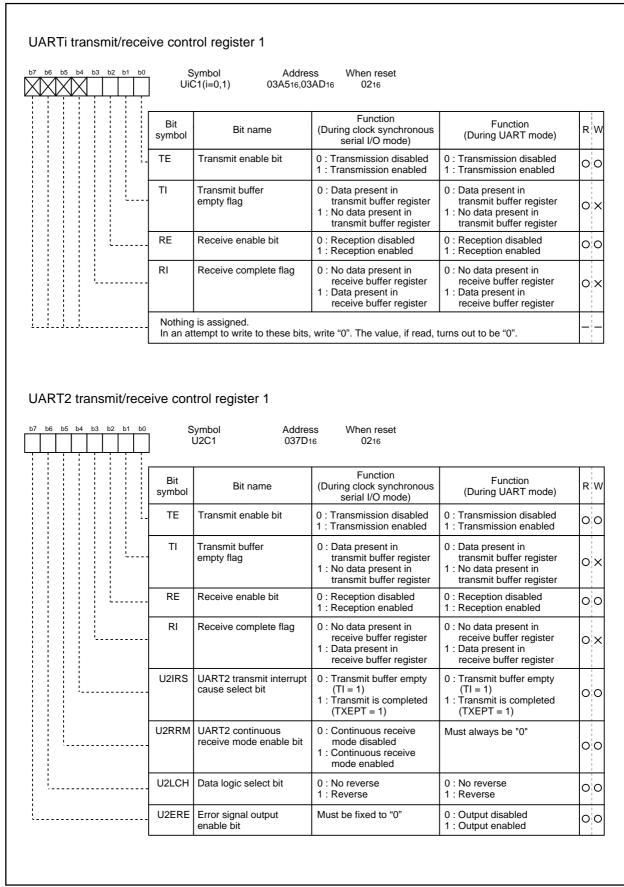

| 2.5.2 Operation of Serial I/O (transmission in UART mode)                                                                                  | 2-84 |

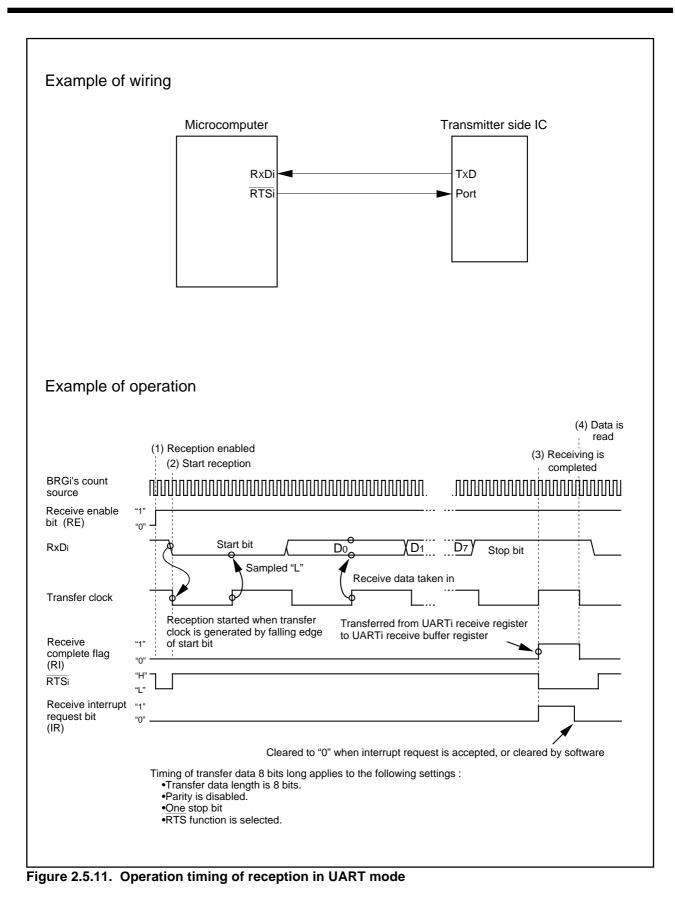

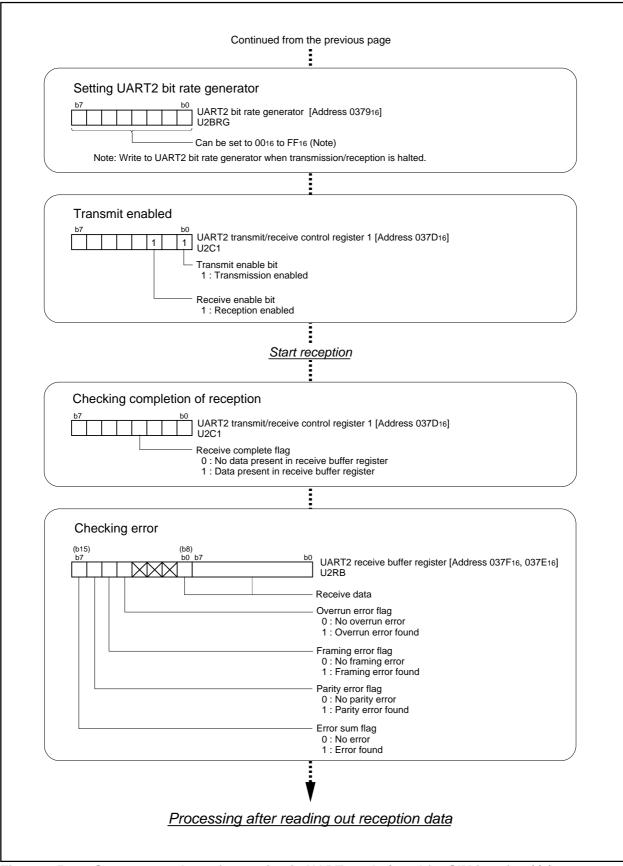

| 2.5.3 Operation of Serial I/O (reception in UART mode)                                                                                     | 2-88 |

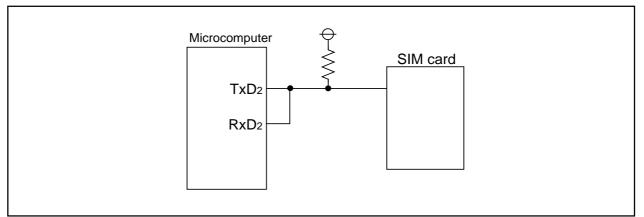

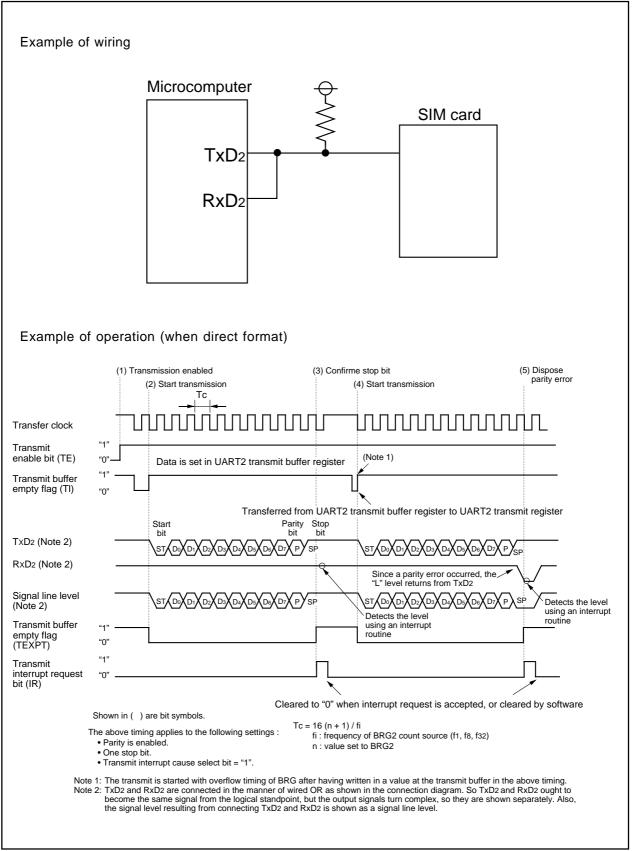

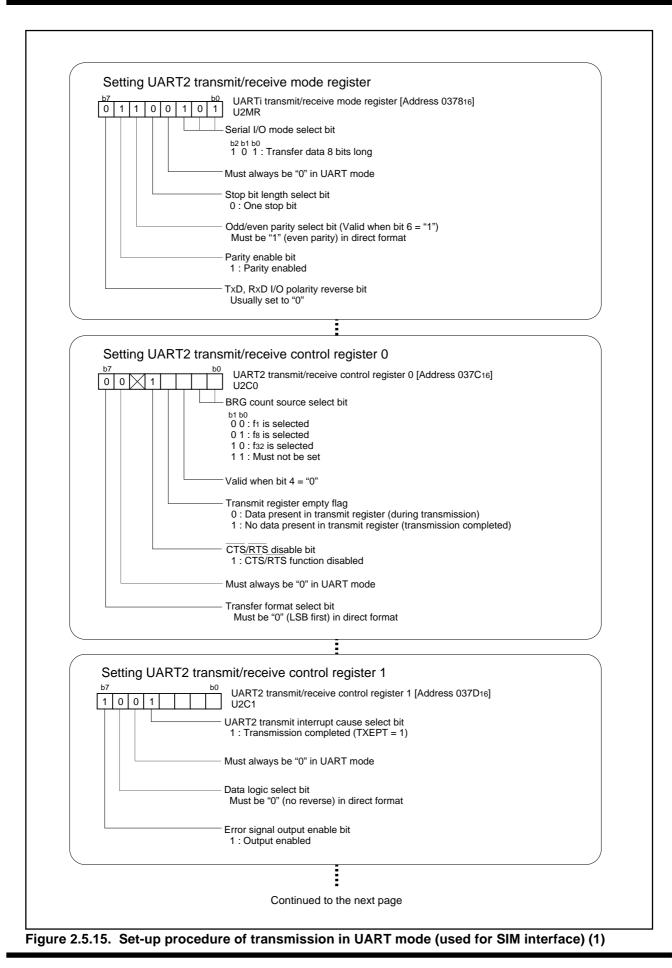

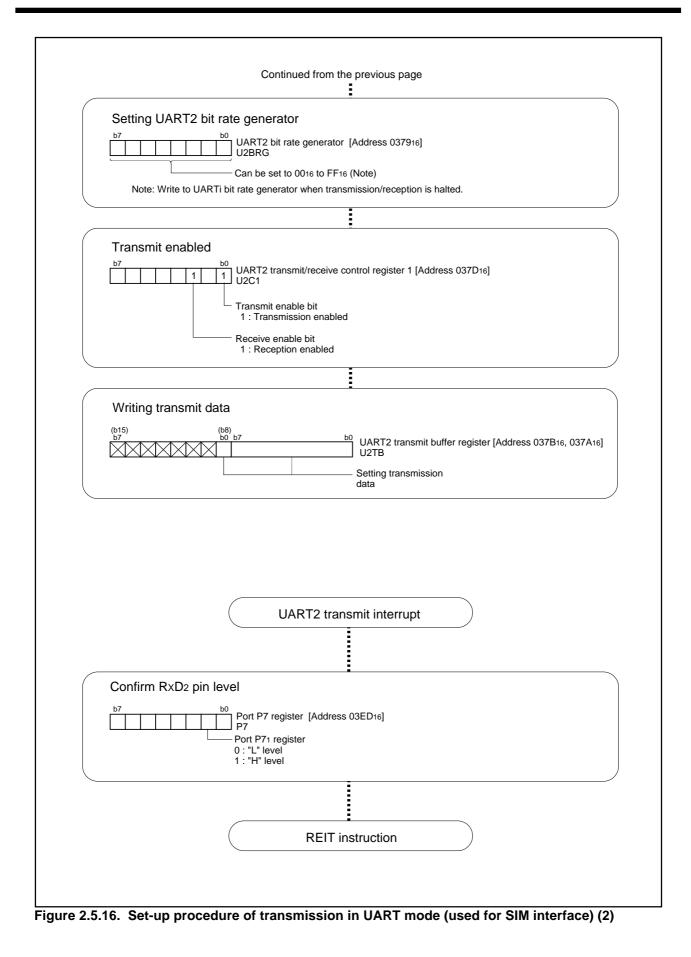

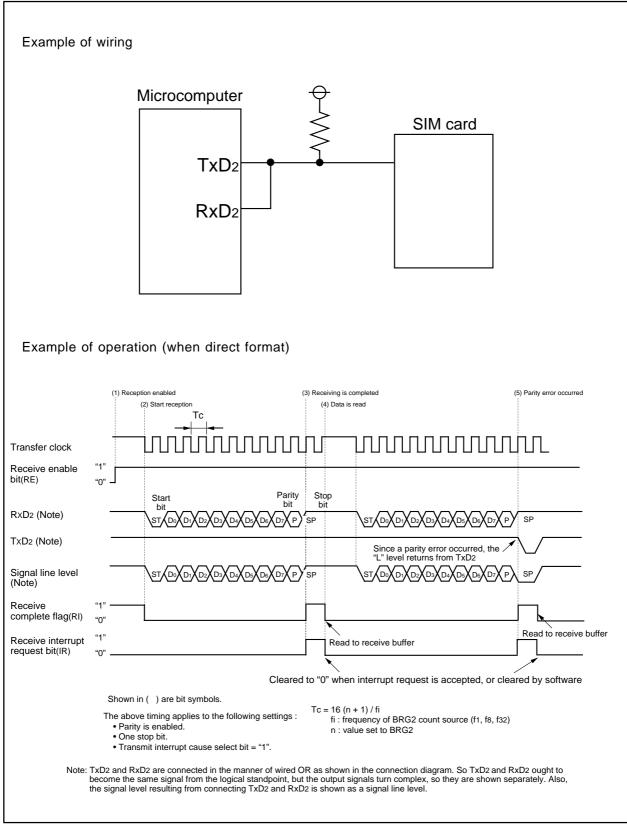

|    | 2.5.4 Operation of Serial I/O (transmission used for SIM interface)                      | 2-92   |

|----|------------------------------------------------------------------------------------------|--------|

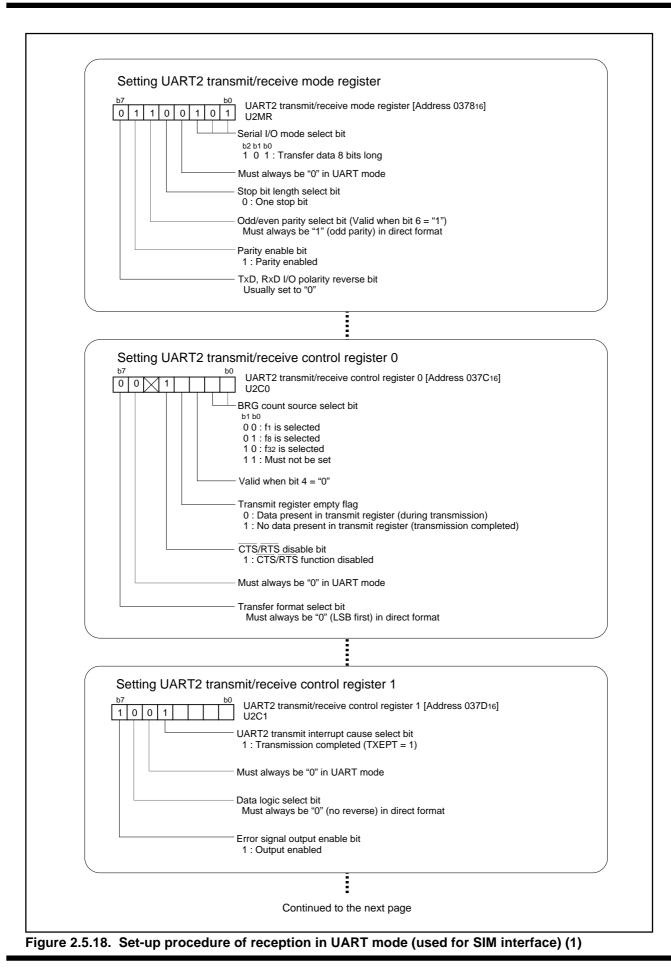

|    | 2.5.5 Operation of Serial I/O (reception used for SIM interface)                         | 2-96   |

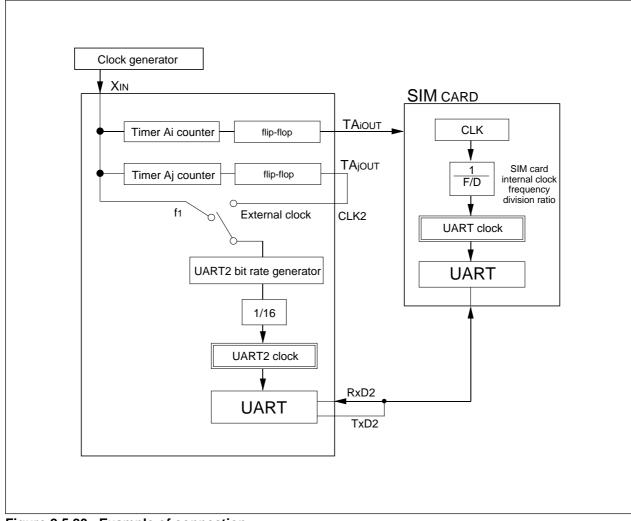

|    | 2.5.6 Clock Signals in used for the SIM Interface                                        | 2-100  |

|    | 2.5.7 Error-permitted range range of transfer baud                                       | 2-104  |

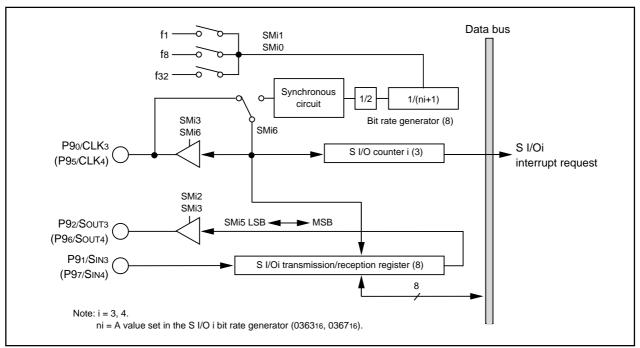

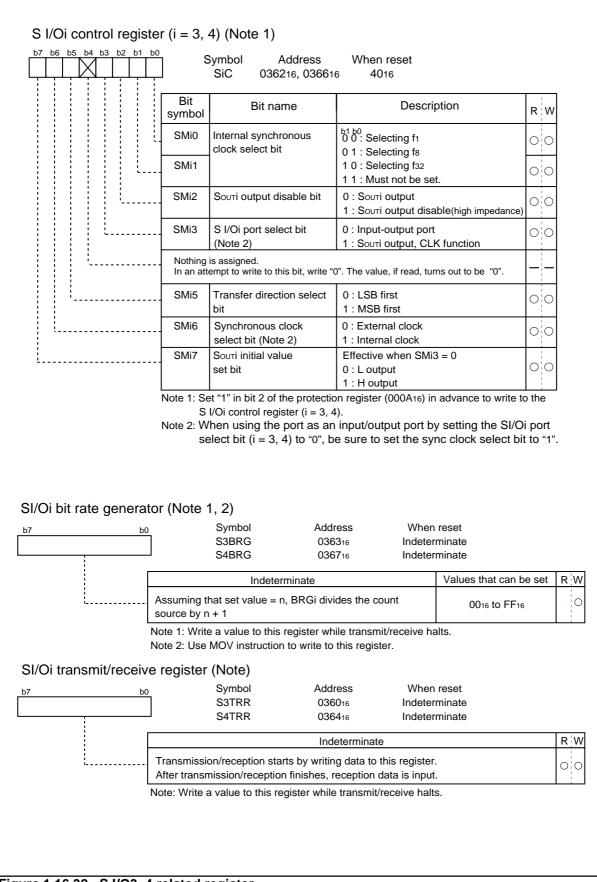

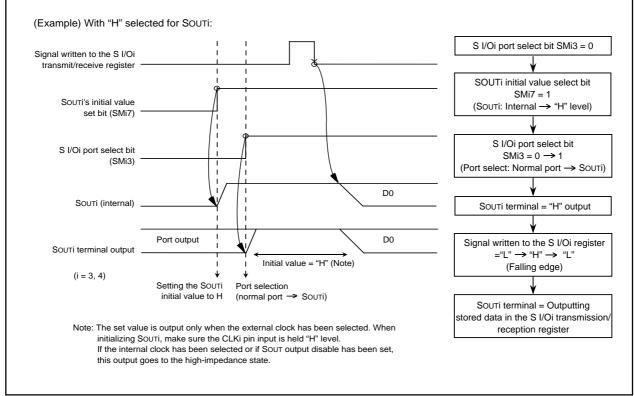

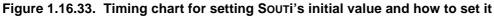

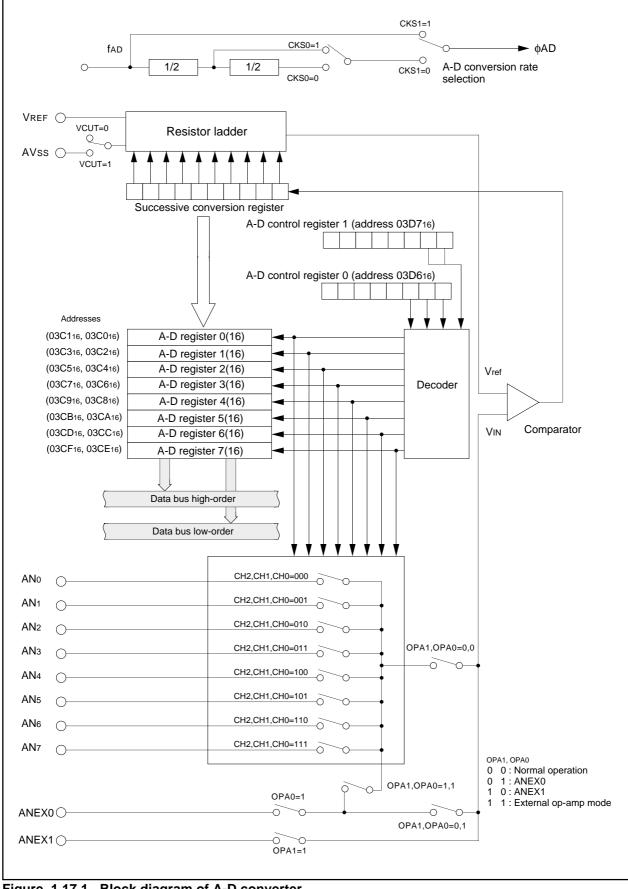

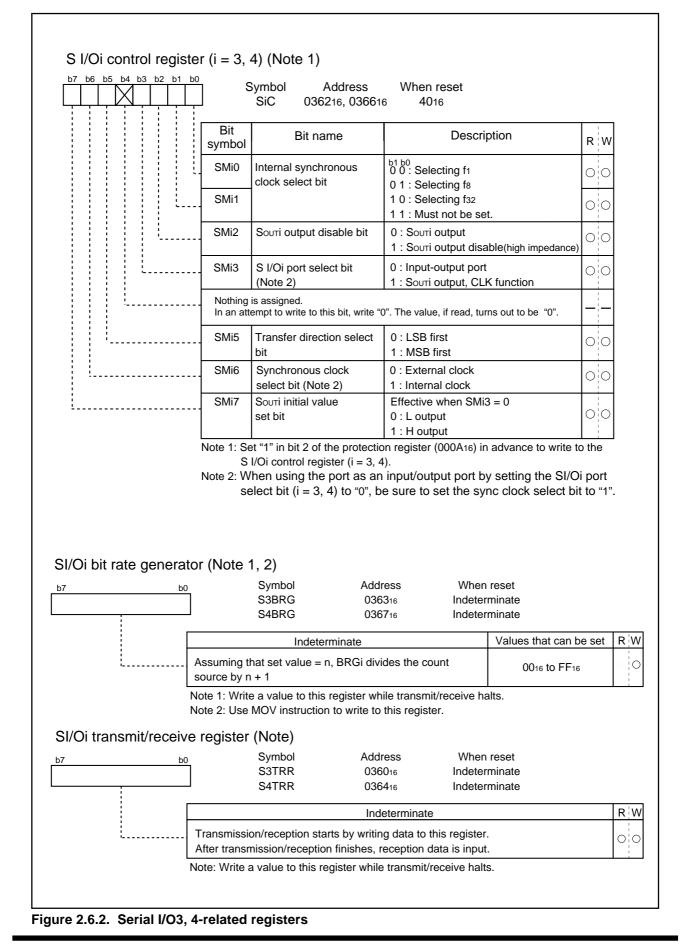

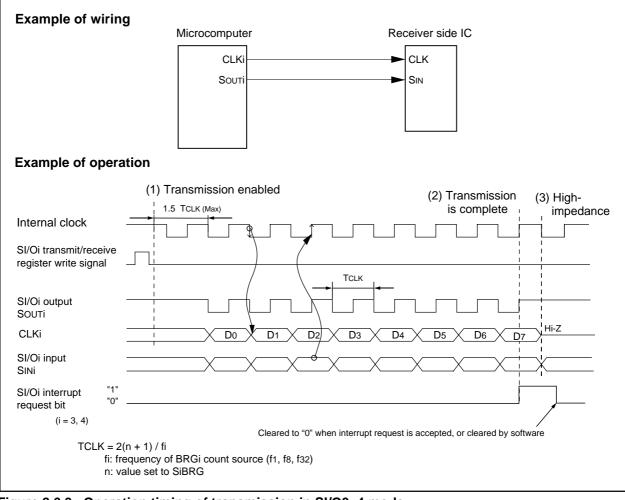

| 2. | 6 SI/O3, 4 Usage                                                                         | 2-106  |

|    | 2.6.1 Overview of the SI/O3,4 usage                                                      | 2-106  |

|    | 2.6.2 Operation of SI/O3,4                                                               | 2-108  |

| 2. | 7 A-D Converter Usage                                                                    | 2-110  |

|    | 2.7.1 Overview of the A-D converter usage                                                | 2-110  |

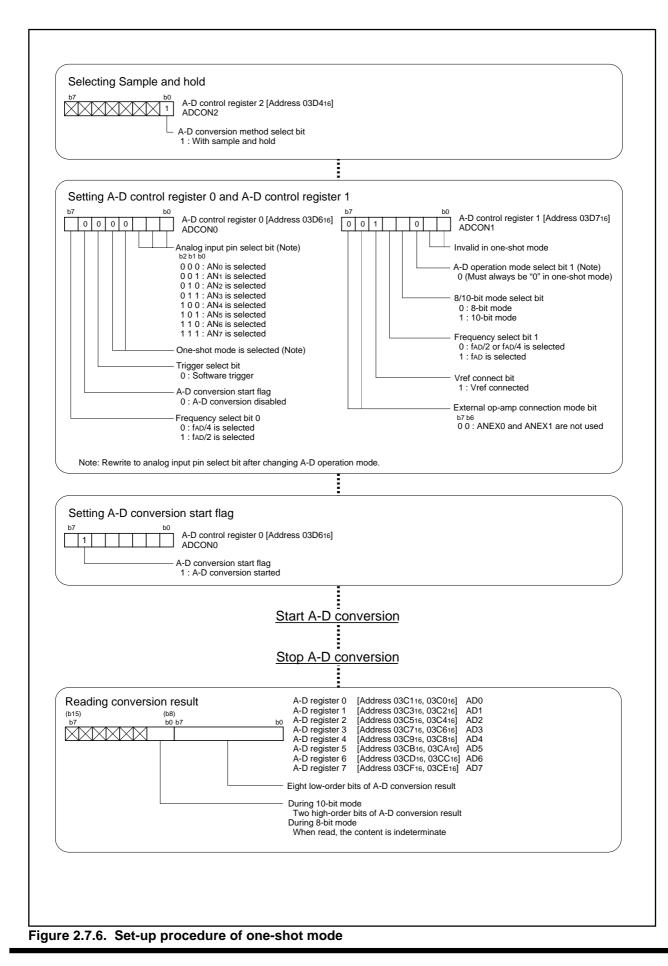

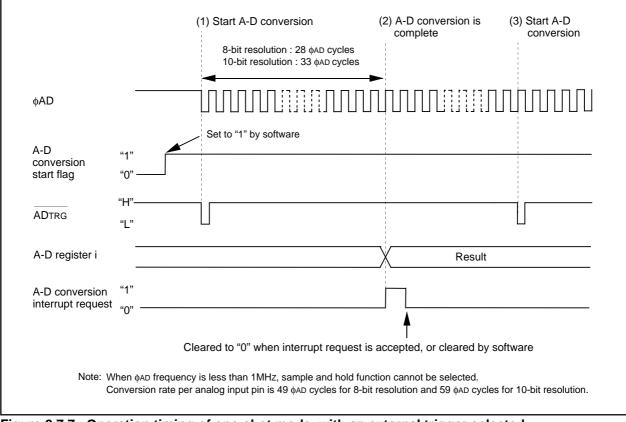

|    | 2.7.2 Operation of A-D converter (one-shot mode)                                         | 2-116  |

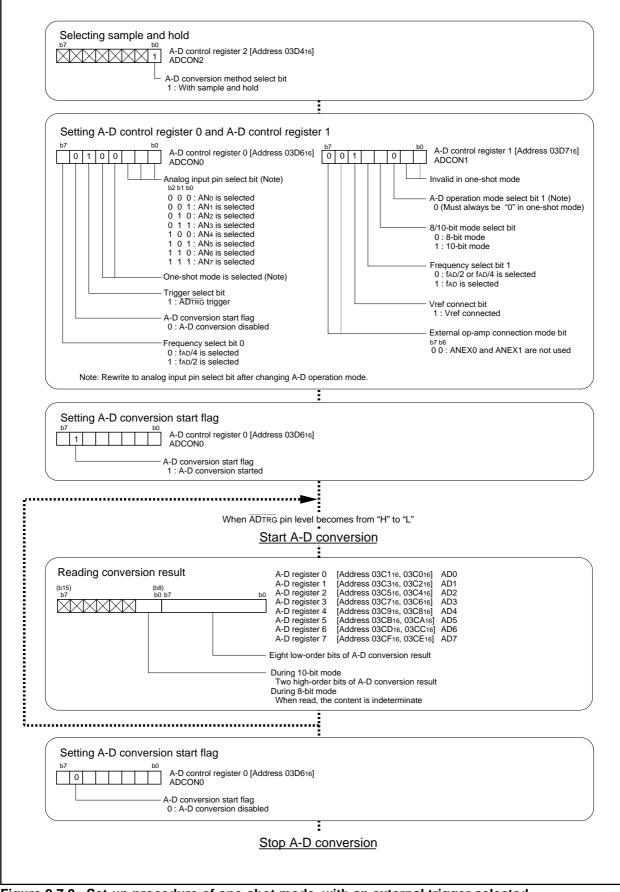

|    | 2.7.3 Operation of A-D Converter (in one-shot mode, an external trigger selected)        | 2-118  |

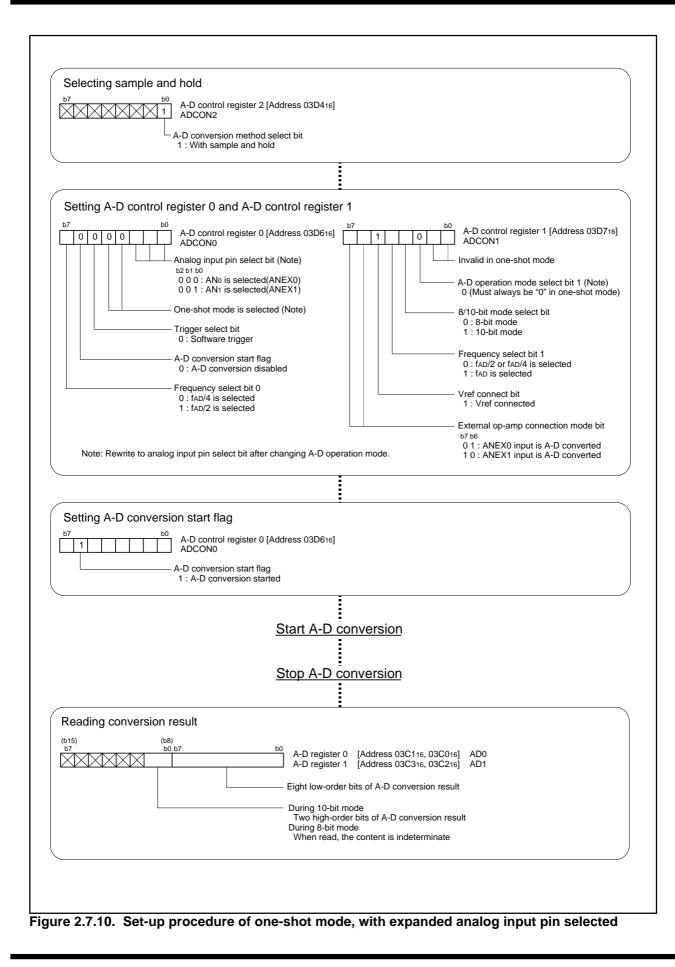

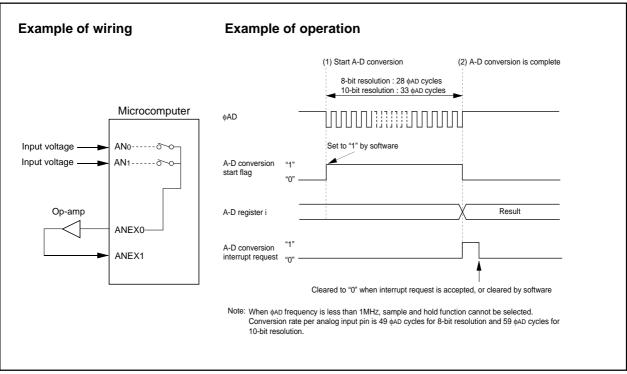

|    | 2.7.4 Operation of A-D Converter (in one-shot mode, expanded analog input pin selected)  | 2-120  |

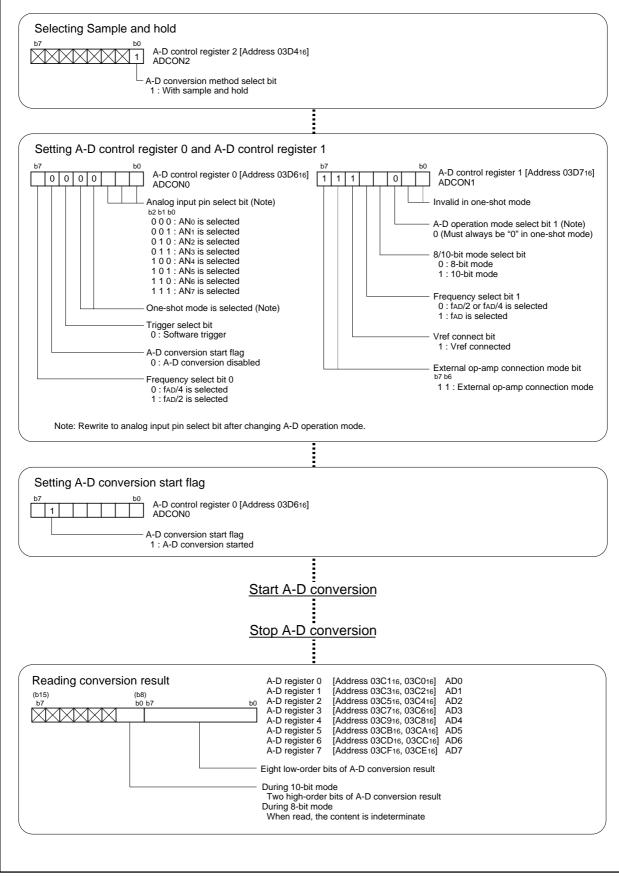

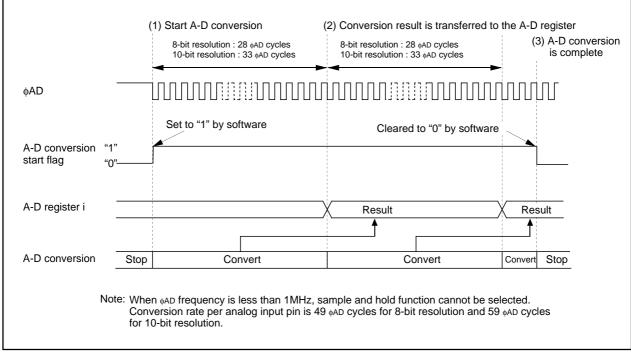

|    | 2.7.5 Operation of A-D Converter (in one-shot mode, external op-amp connection mode sele | cted). |

|    |                                                                                          | 2-122  |

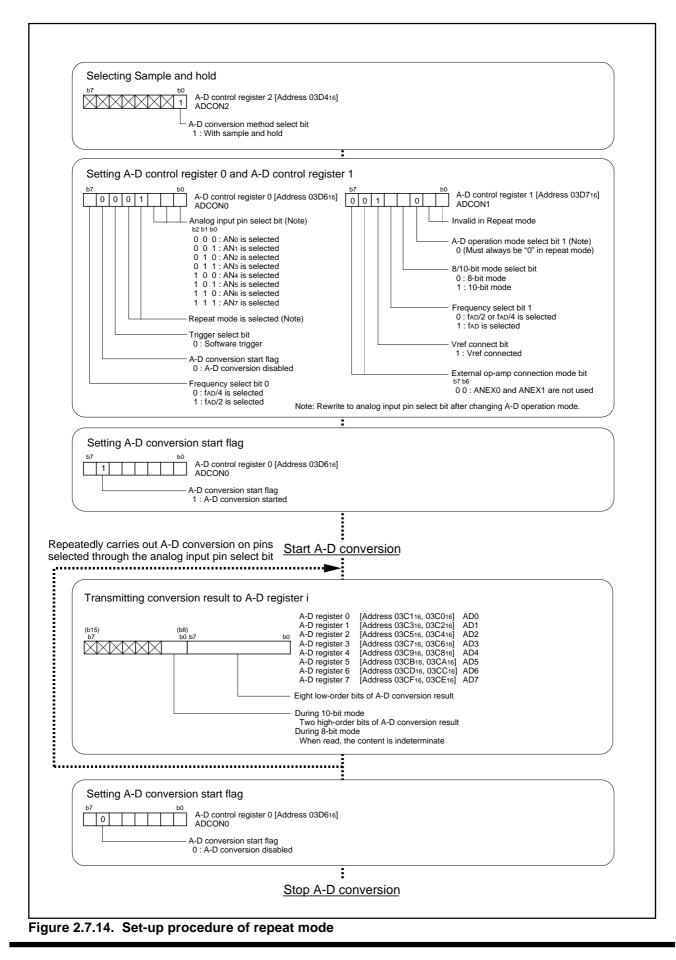

|    | 2.7.6 Operation of A-D Converter (in repeat mode)                                        | 2-124  |

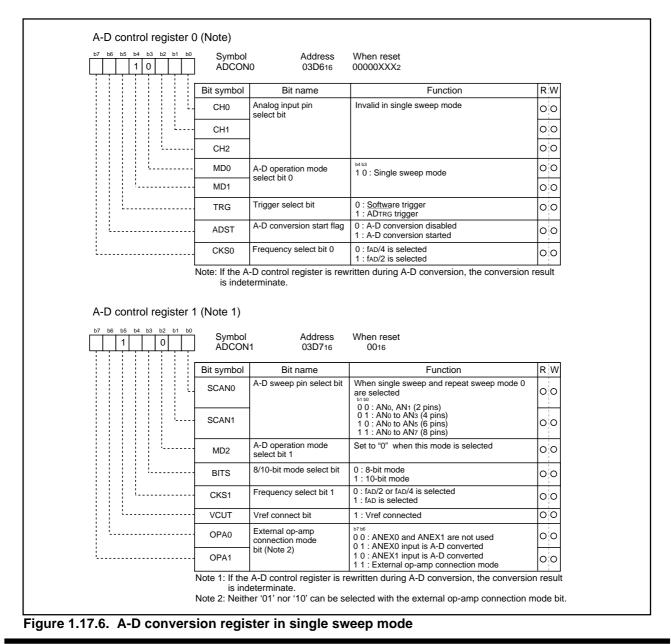

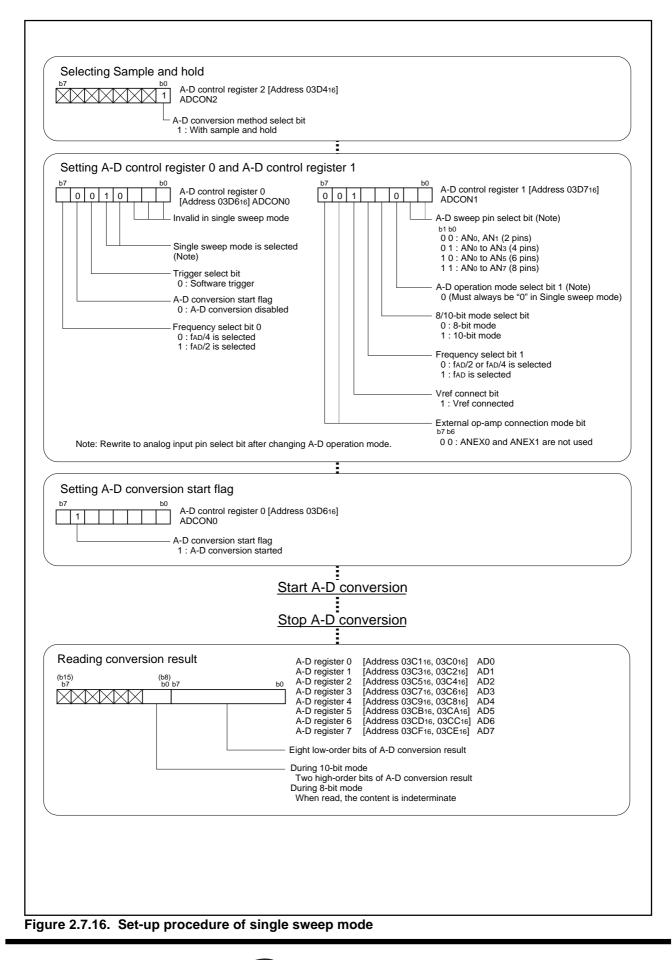

|    | 2.7.7 Operation of A-D Converter (in single sweep mode)                                  | 2-126  |

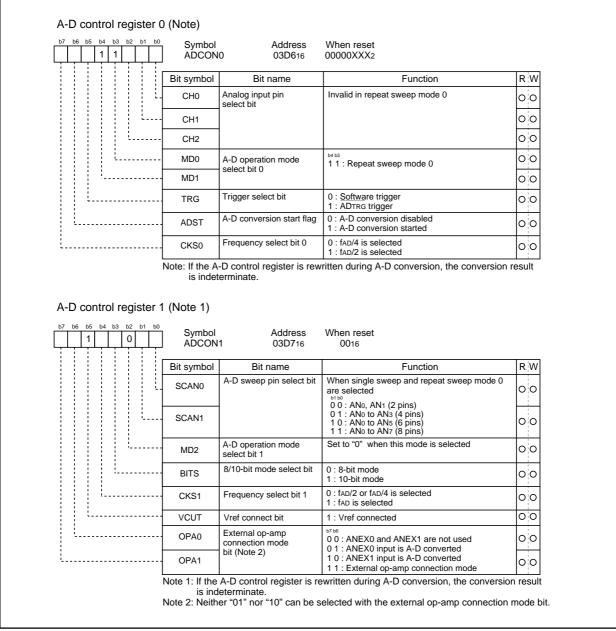

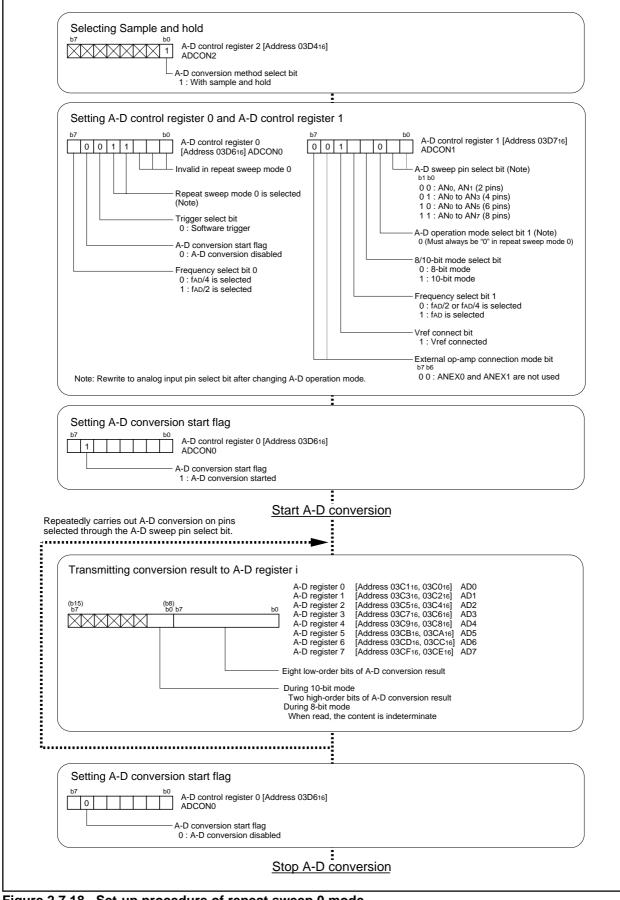

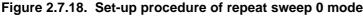

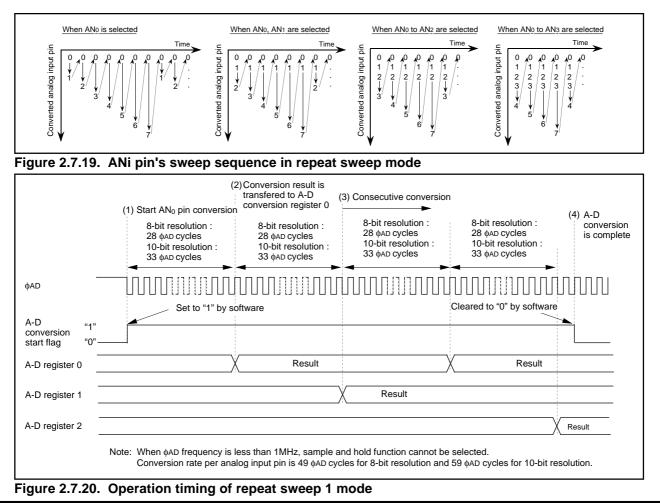

|    | 2.7.8 Operation of A-D Converter (in repeat sweep mode 0)                                | 2-128  |

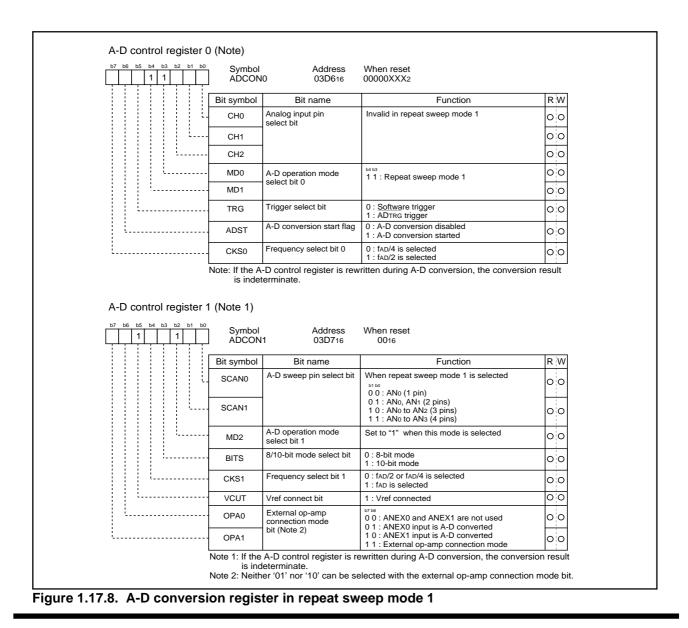

|    | 2.7.9 Operation of A-D Converter (in repeat sweep mode 1)                                | 2-130  |

|    | 2.7.10 Precautions for A-D Converter                                                     | 2-132  |

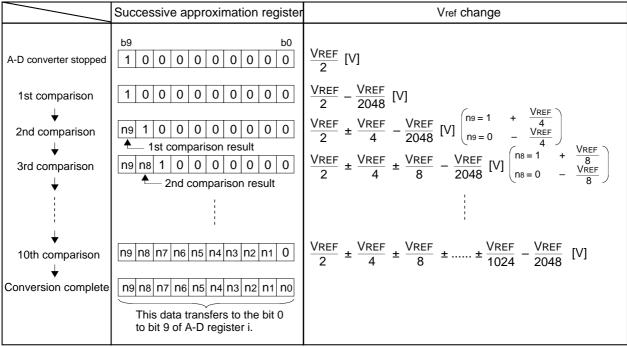

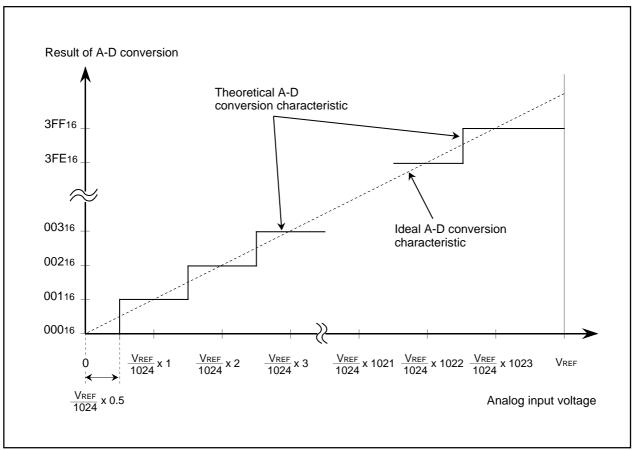

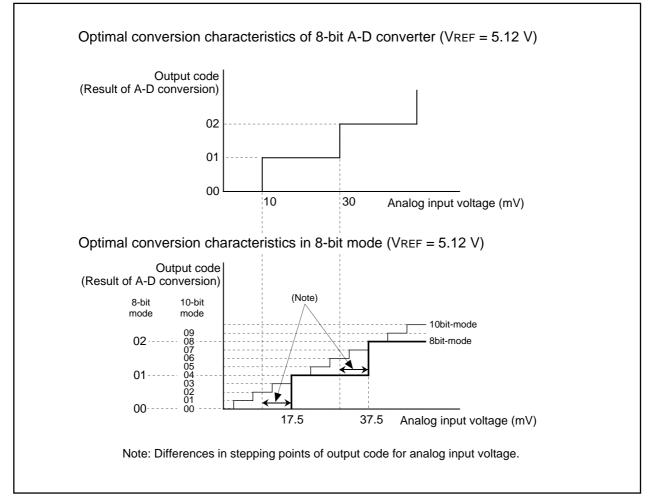

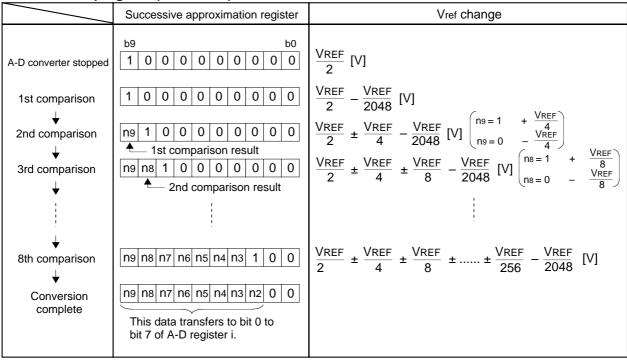

|    | 2.7.11 Method of A-D Conversion (10-bit mode)                                            | 2-133  |

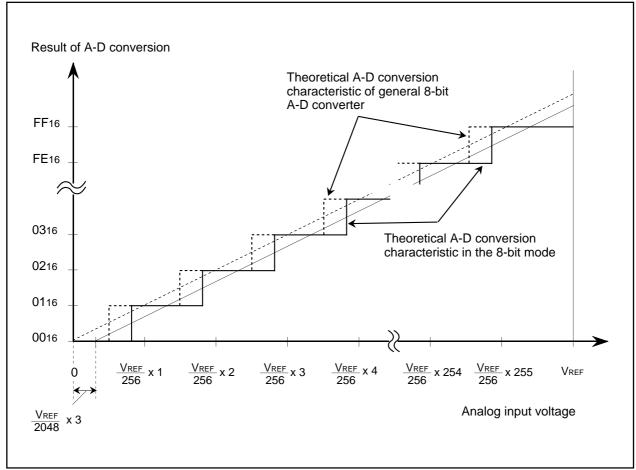

|    | 2.7.12 Method of A-D Conversion (8-bit mode)                                             | 2-135  |

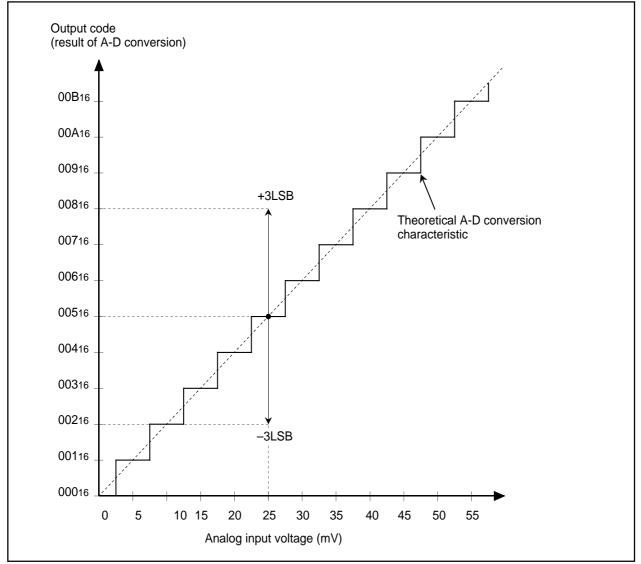

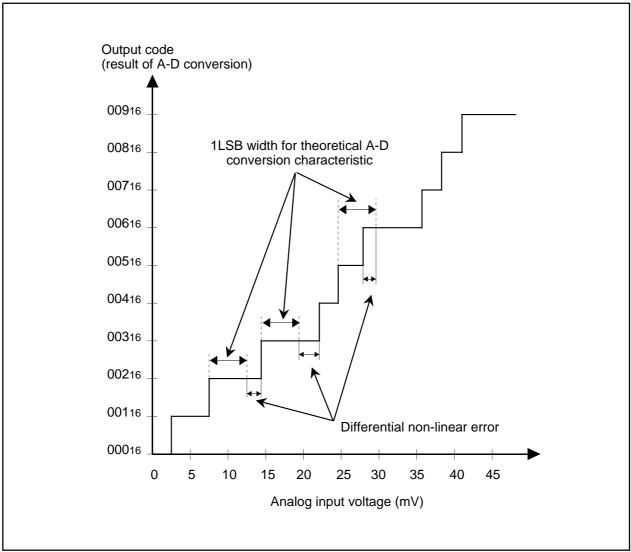

|    | 2.7.13 Absolute Accuracy and Differential Non-Linearity Error                            | 2-137  |

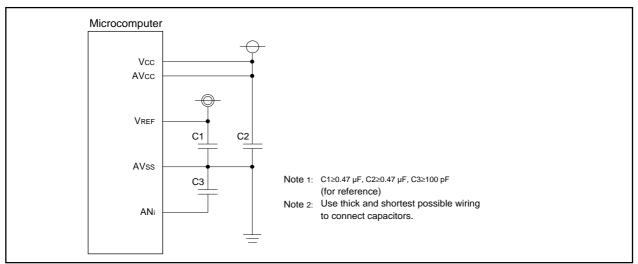

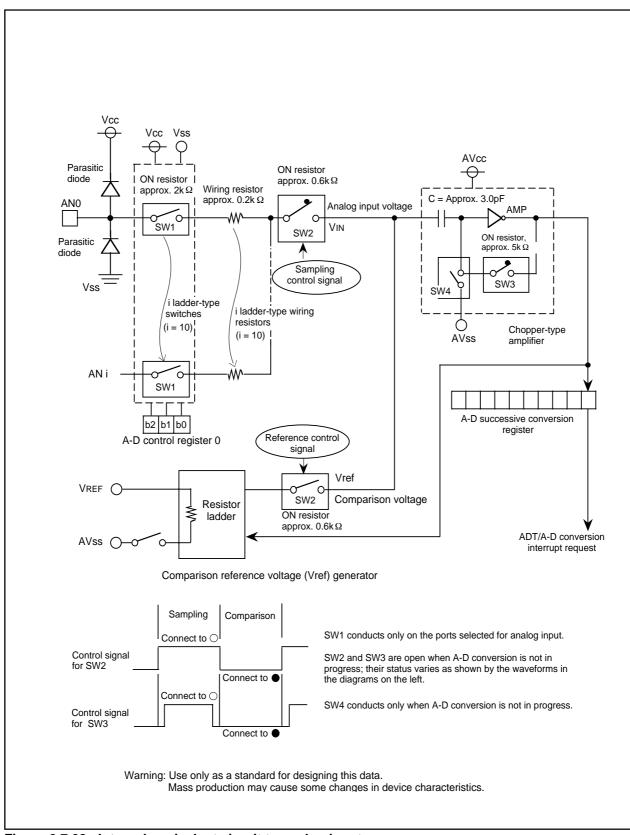

|    | 2.7.14 Internal Equivalent Circuit of Analog Input                                       | 2-139  |

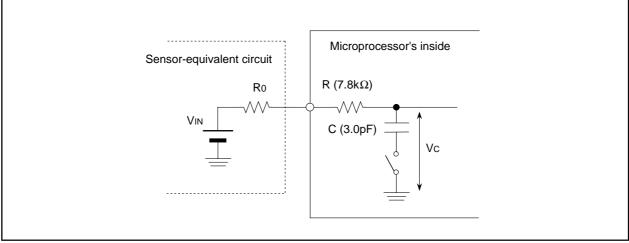

|    | 2.7.15 Sensor's Output Impedance under A-D Conversion                                    | 2-140  |

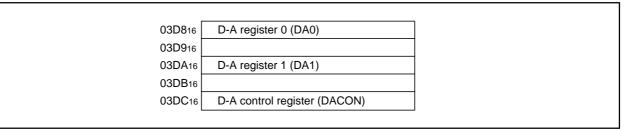

| 2. | 8 D-A Converter Usage                                                                    | 2-142  |

|    | 2.8.1 Overview of the D-A converter usage                                                | 2-142  |

|    | 2.8.2 D-A Converter Operation                                                            | 2-143  |

| 2. | 9 DMAC Usage                                                                             | 2-144  |

|    | 2.9.1 Overview of the DMAC usage                                                         | 2-144  |

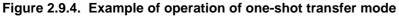

|    | 2.9.2 Operation of DMAC (one-shot transfer mode)                                         | 2-148  |

|    | 2.9.3 Operation of DMAC (repeated transfer mode)                                         | 2-150  |

| 2. | 10 CRC Calculation Circuit Usage                                                         | 2-152  |

|    | 2.10.1 Overview of the CRC calculation circuit usage                                     | 2-152  |

|    | 2.10.2 Operation of CRC Calculation Circuit                                              | 2-153  |

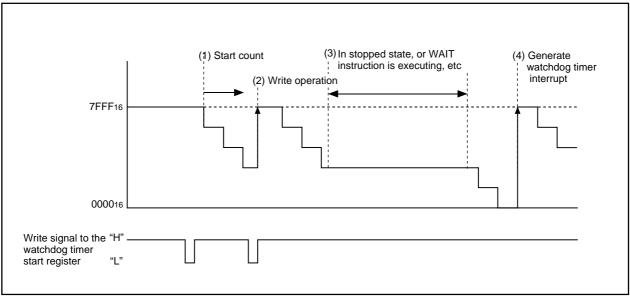

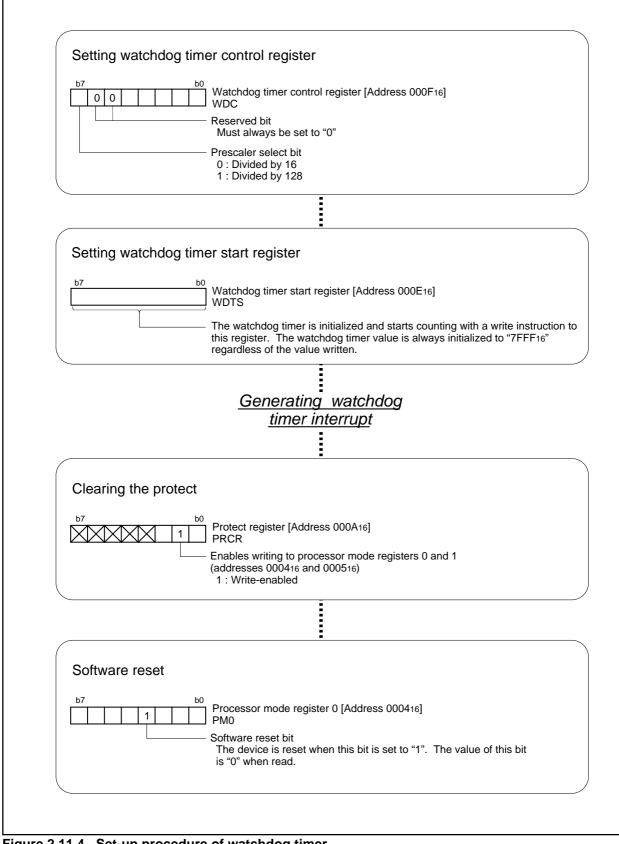

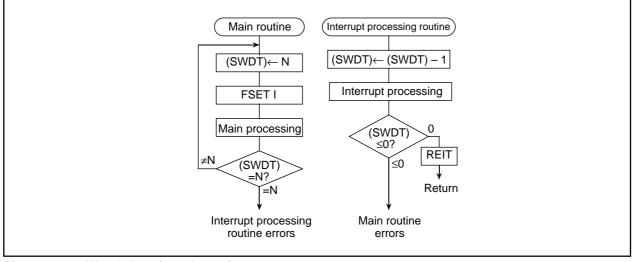

| 2. | 11 Watchdog Timer Usage                                                                  | 2-154  |

| 2.11.1 Overview of the watchdog timer usage          | 2-154 |

|------------------------------------------------------|-------|

| 2.11.2 Operation of Watchdog Timer                   | 2-156 |

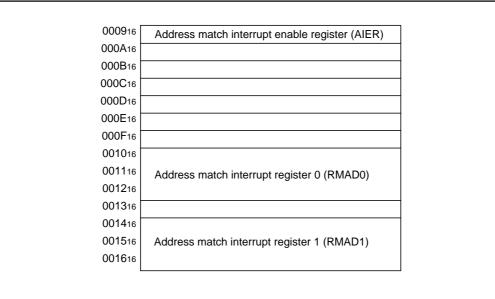

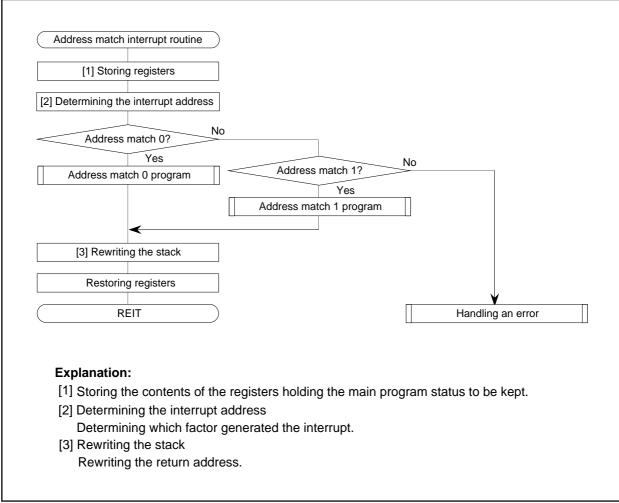

| 2.12 Address Match Interrupt Usage                   | 2-158 |

| 2.12.1 Overview of the address match interrupt usage | 2-158 |

| 2.12.2 Operation of Address Match Interrupt          | 2-160 |

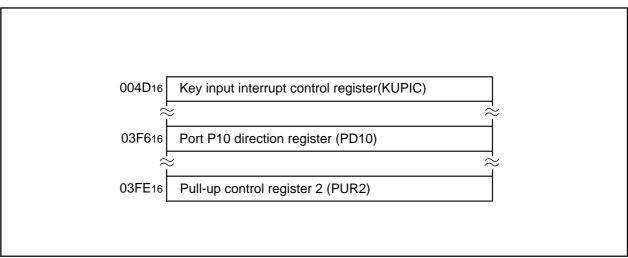

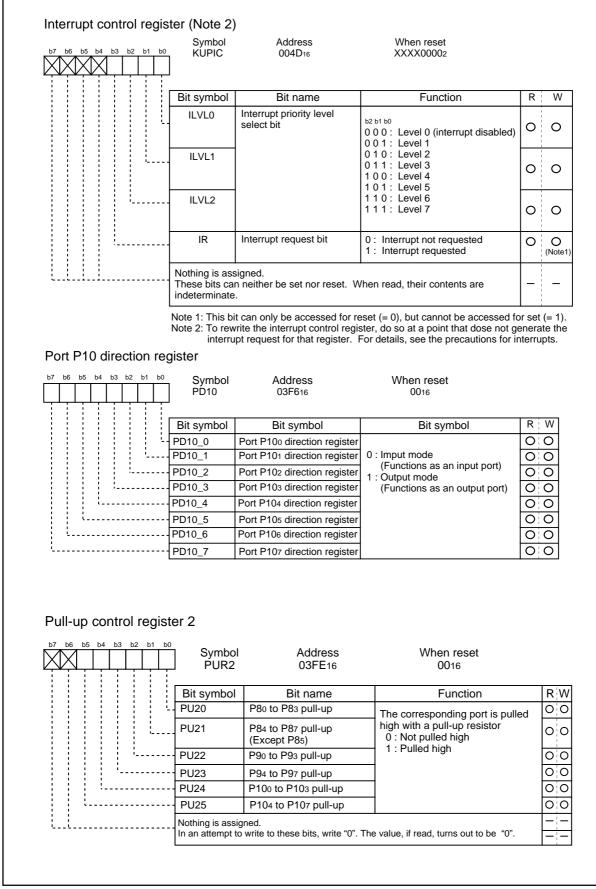

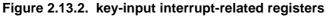

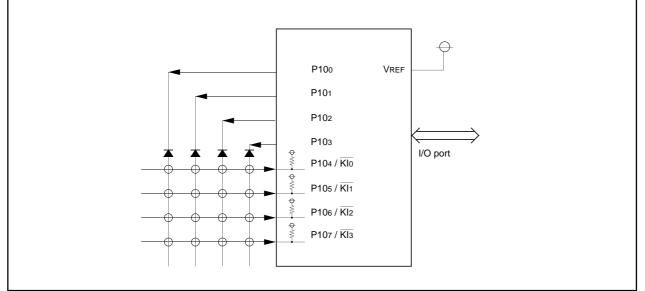

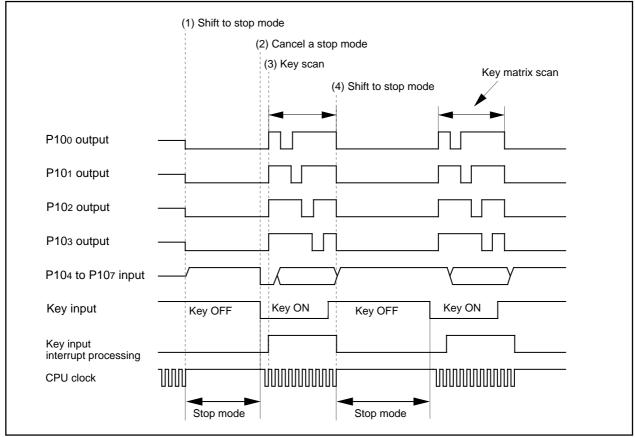

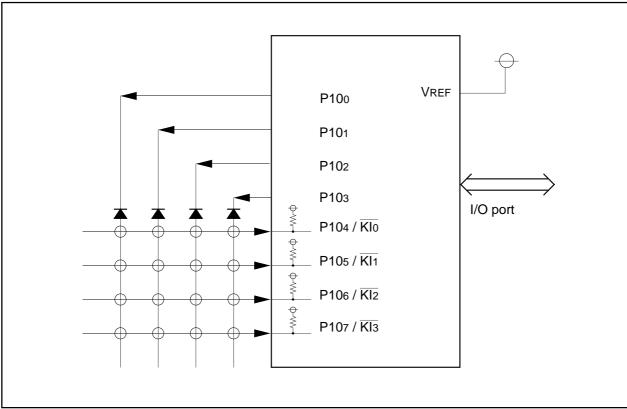

| 2.13 Key-Input Interrupt Usage                       | 2-162 |

| 2.13.1 Overview of the key-input interrupt usage     | 2-162 |

| 2.13.2 Operation of Key-Input Interrupt              | 2-164 |

| 2.14 Multiple interrupts usage                       | 2-166 |

| 2.14.1 Overview of the Multiple interrupts usage     | 2-166 |

| 2.14.2 Multiple Interrupts operation                 | 2-171 |

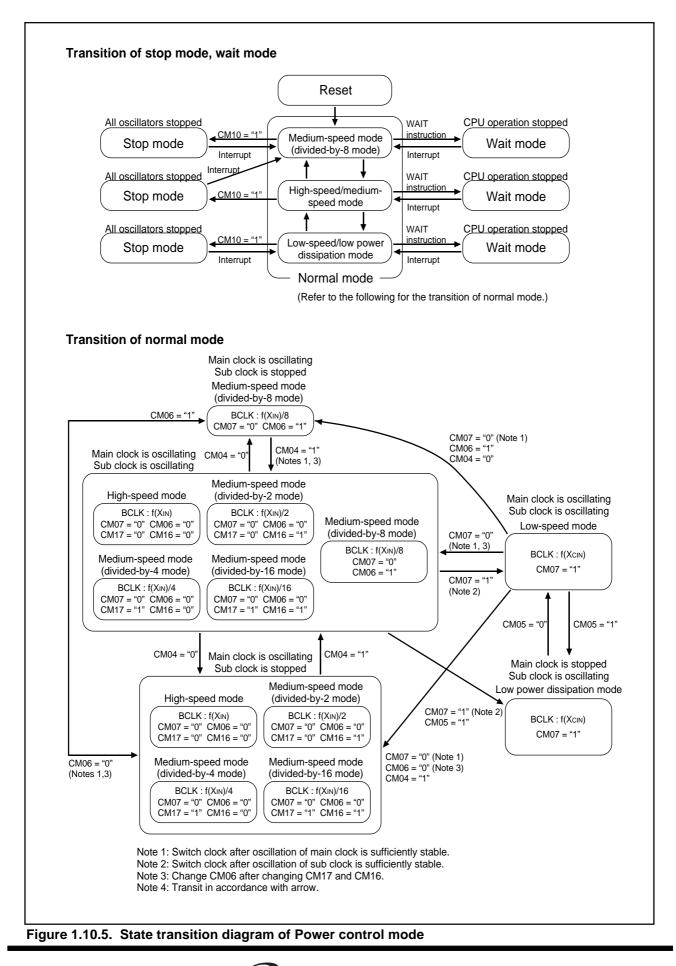

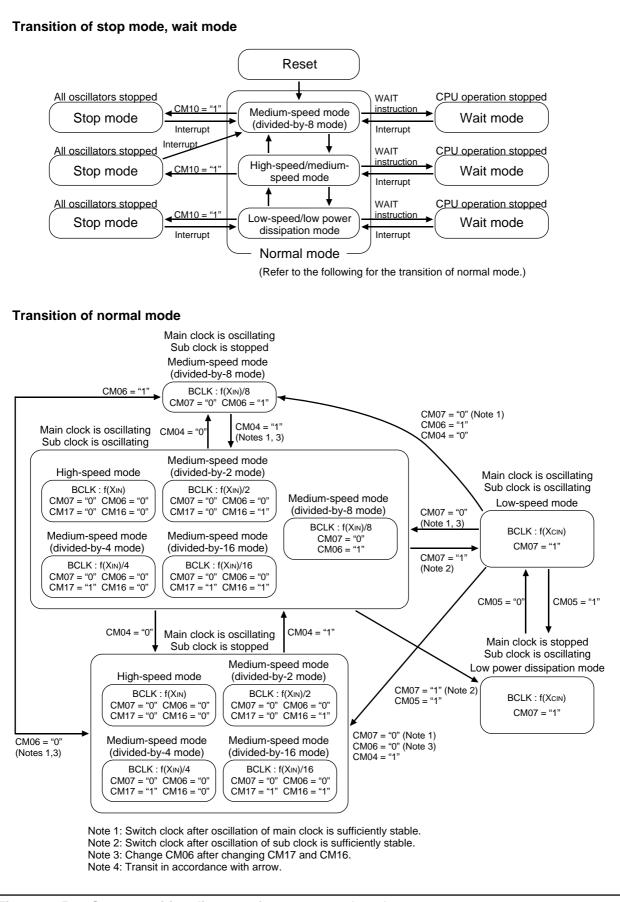

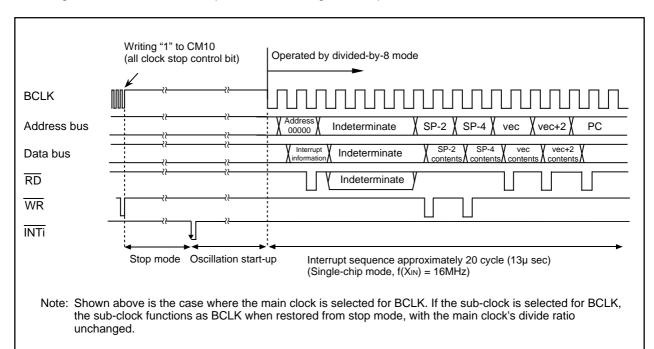

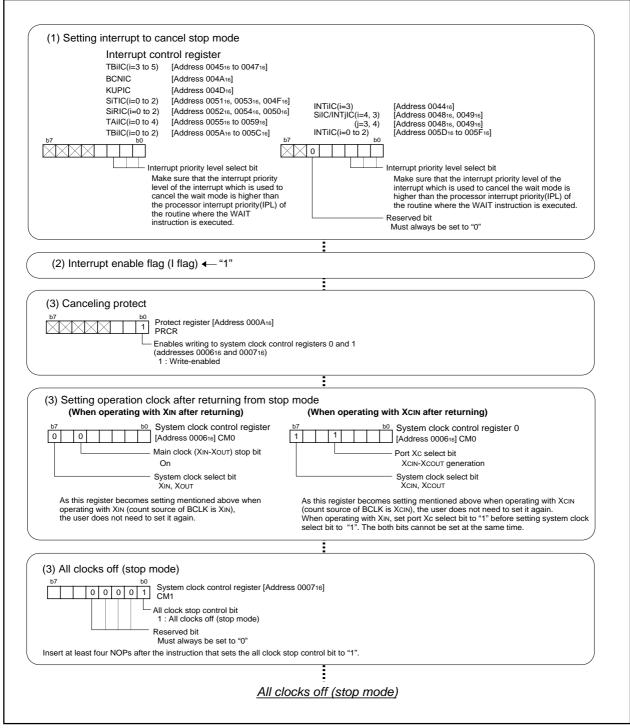

| 2.15 Power Control Usage                             | 2-173 |

| 2.15.1 Overview of the power control usage           | 2-173 |

| 2.15.2 Stop Mode Set-Up                              | 2-178 |

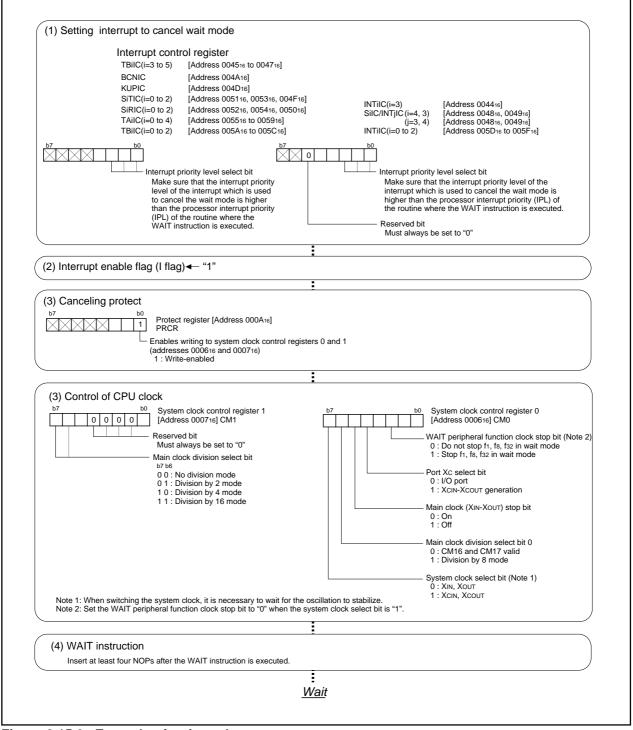

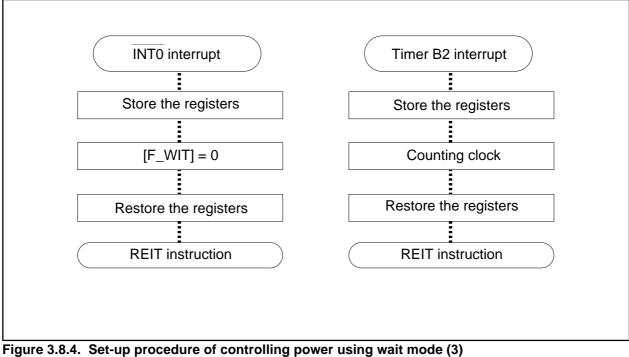

| 2.15.3 Wait Mode Set-Up                              | 2-179 |

| 2.15.4 Precautions in Power Control                  | 2-180 |

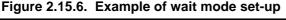

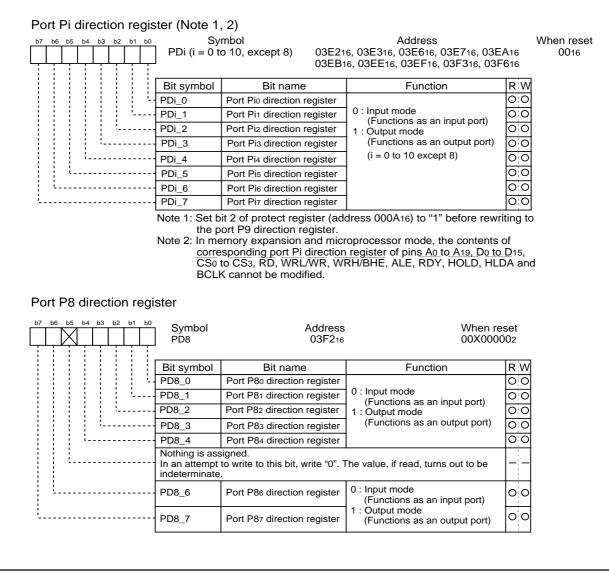

| 2.16 Programmable I/O Ports Usage                    | 2-181 |

| 2.16.1 Overview of the programmable I/O ports usage  | 2-181 |

### Chapter 3 Examples of Peripheral functions Applications \_\_\_\_\_

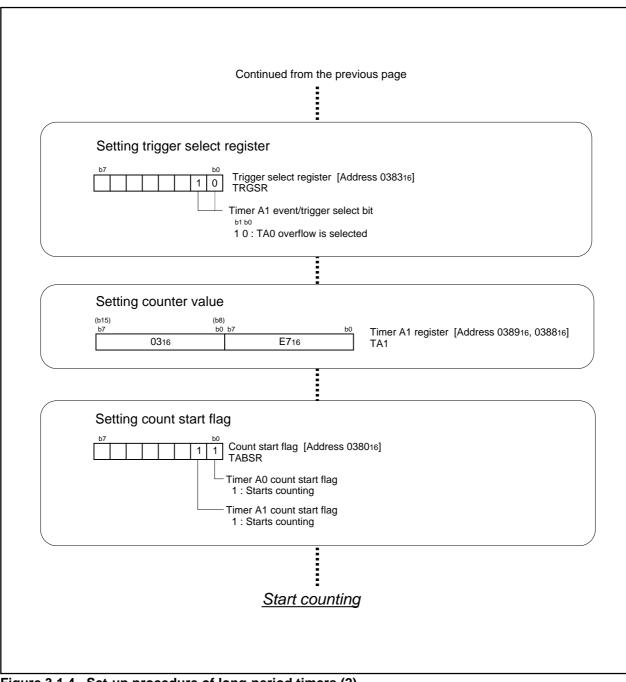

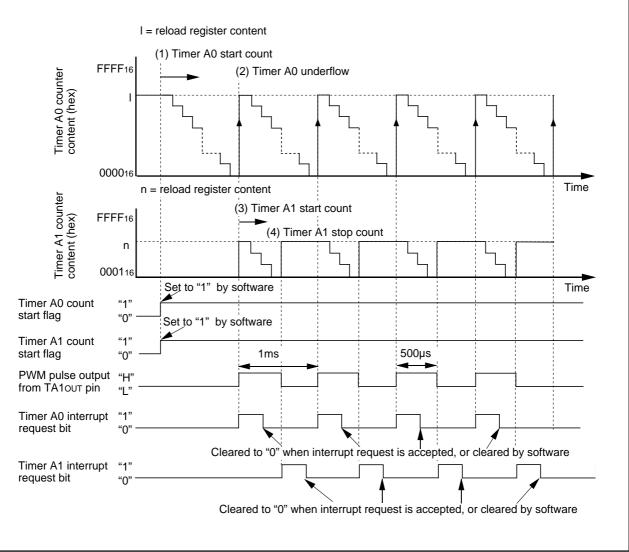

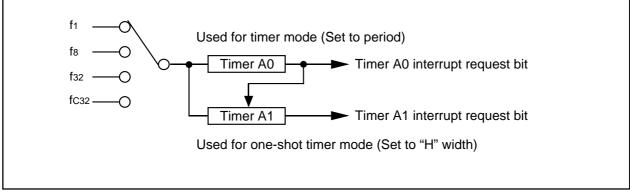

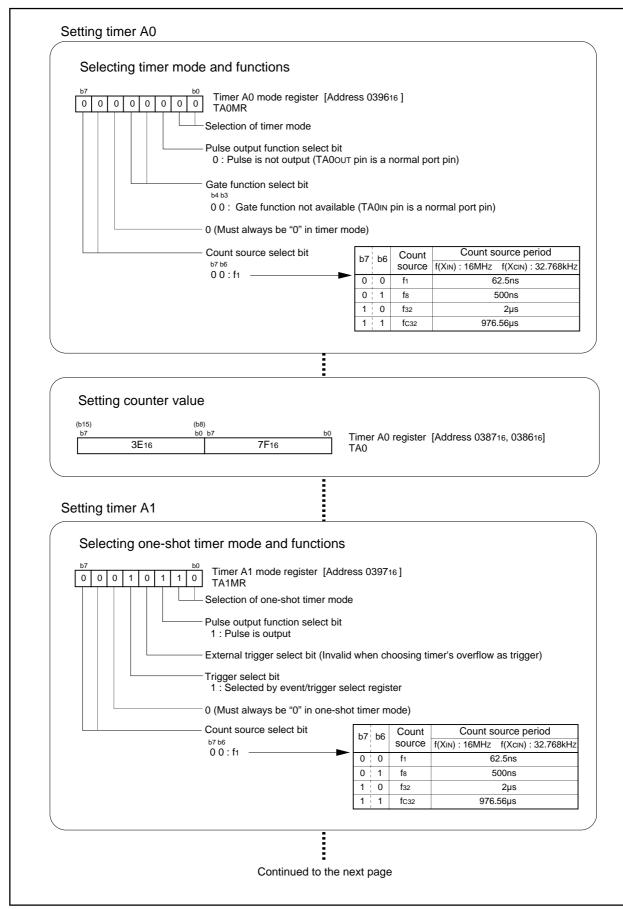

| 3.1 Long-Period Timers                            |

|---------------------------------------------------|

| 3.2 Variable-Period Variable-Duty PWM Output      |

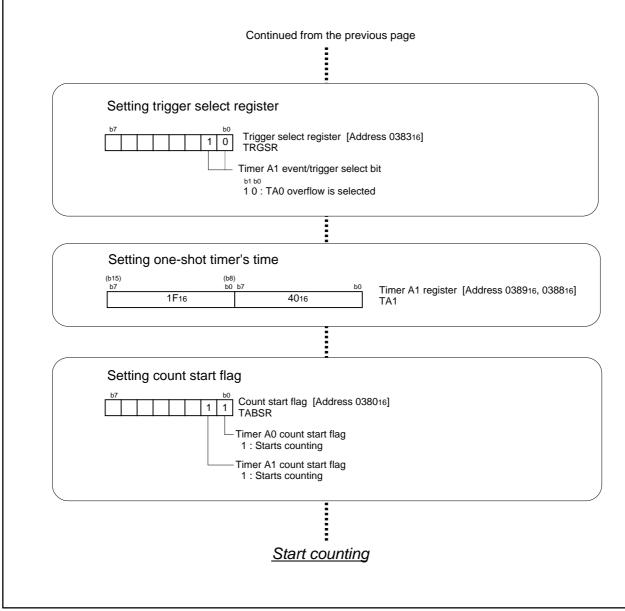

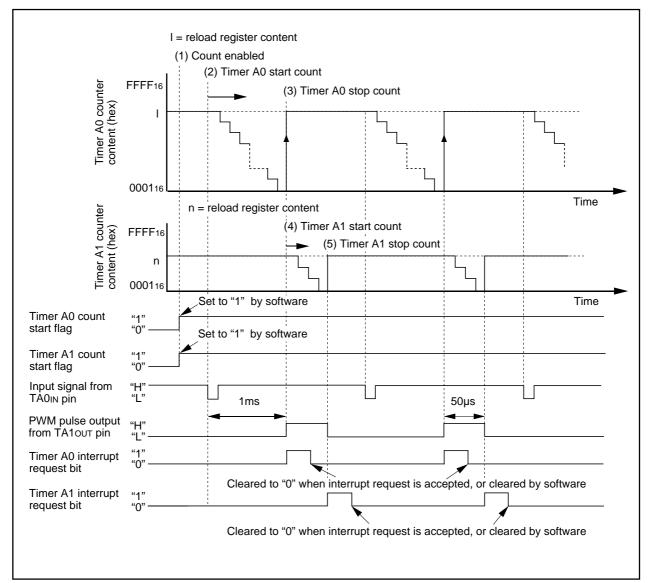

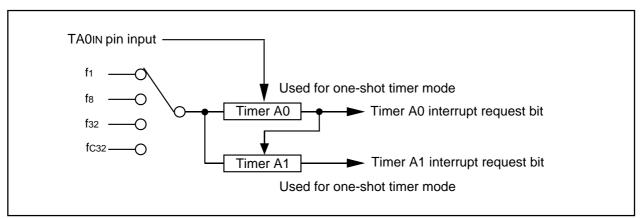

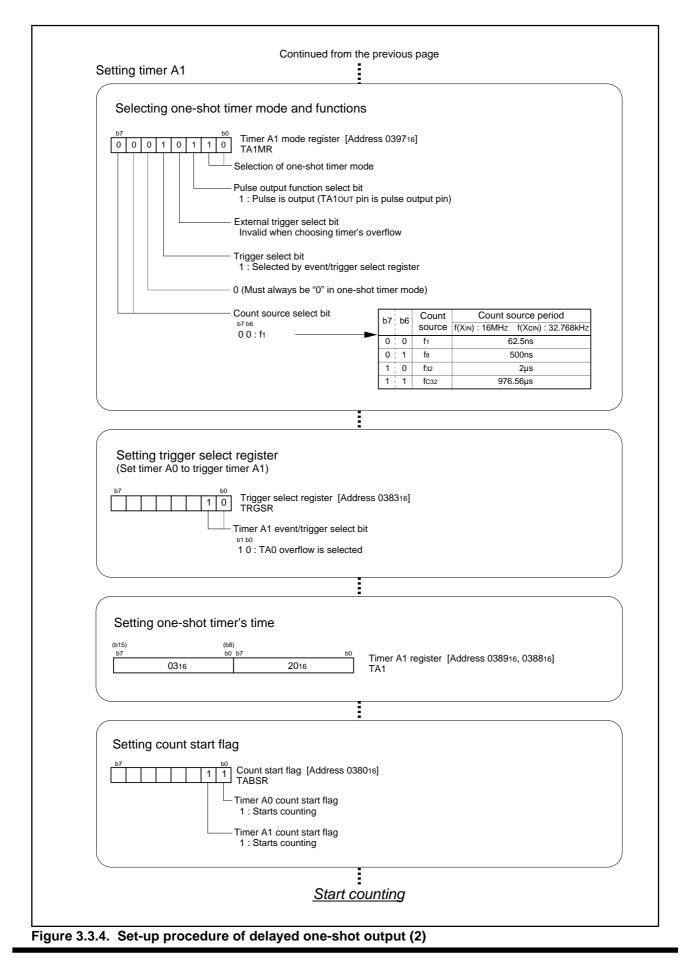

| 3.3 Delayed One-Shot Output 2-200                 |

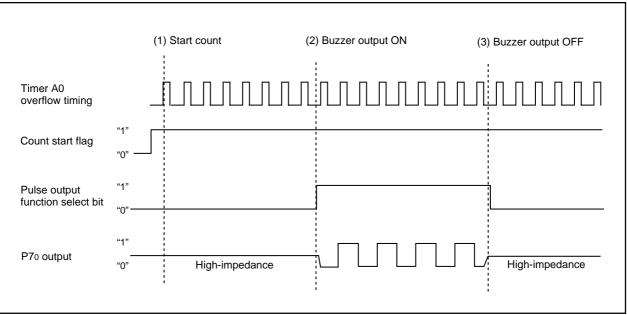

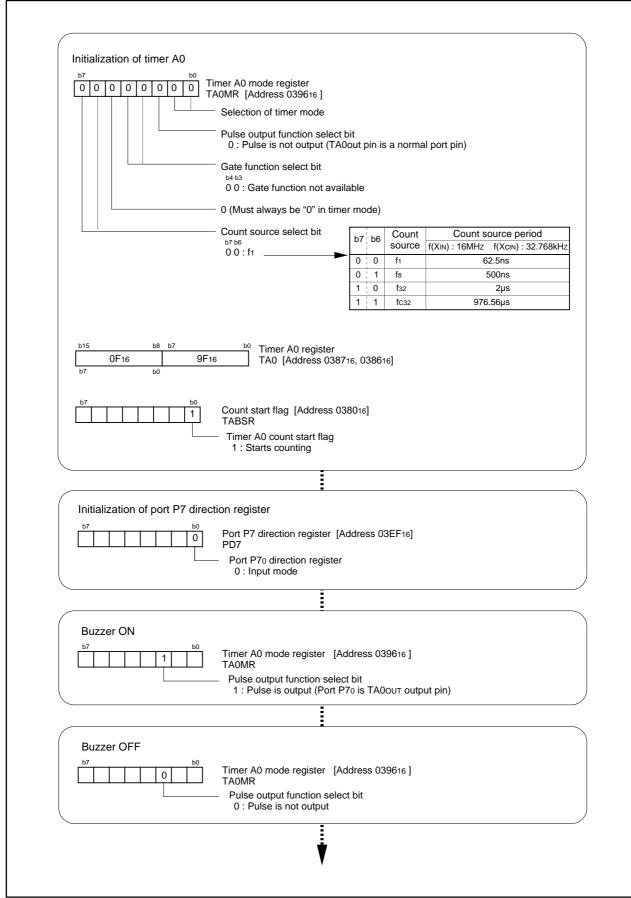

| 3.4 Buzzer Output                                 |

| 3.5 Solution for External Interrupt Pins Shortage |

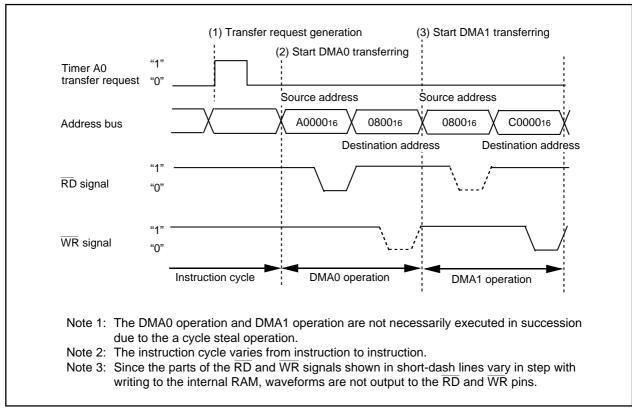

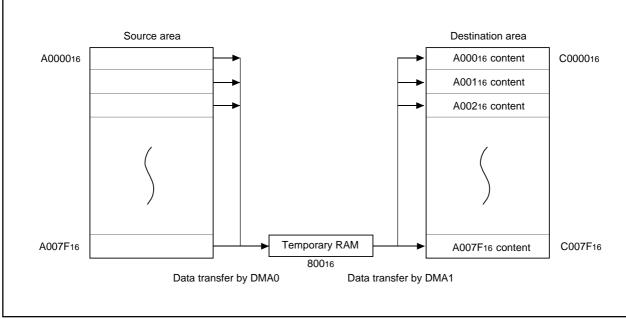

| 3.6 Memory to Memory DMA Transfer                 |

| 3.7 Controlling Power Using Stop Mode             |

| 3.8 Controling Power Using Wait Mode 2-210        |

### Chapter 4 External Buses \_\_\_\_\_

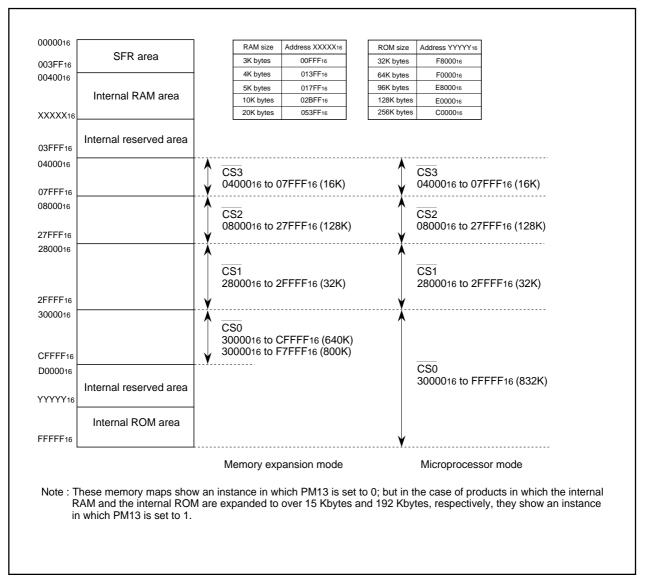

| 4.1 Overview of External Buses 2     | 2-222 |

|--------------------------------------|-------|

| 4.2 Data Access                      | 2-223 |

| 4.2.1 Data Bus Width 2               | 2-223 |

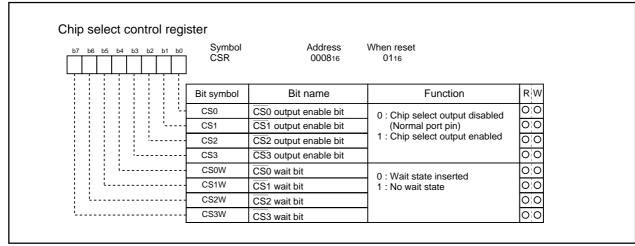

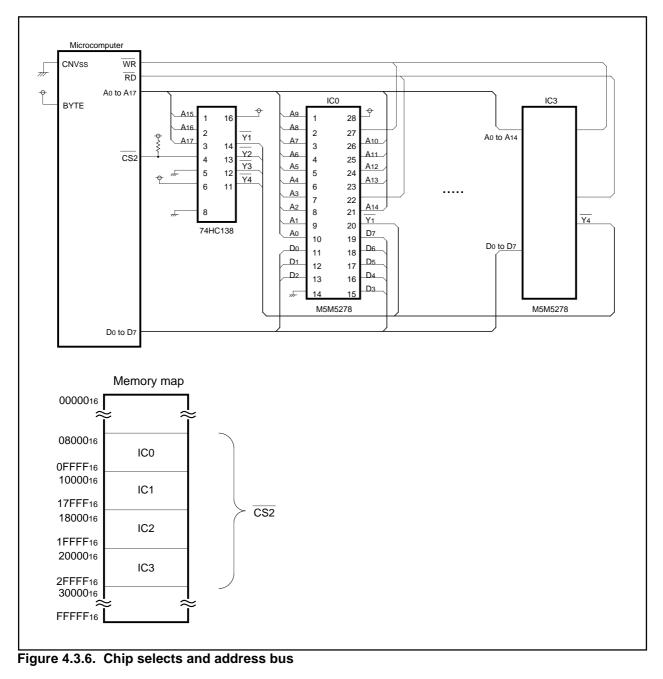

| 4.2.2 Chip Selects and Address Bus 2 | 2-224 |

| 4.2.3 Bus Types                      | 2-225 |

| 4.2.4 R/W Modes                      | 225   |

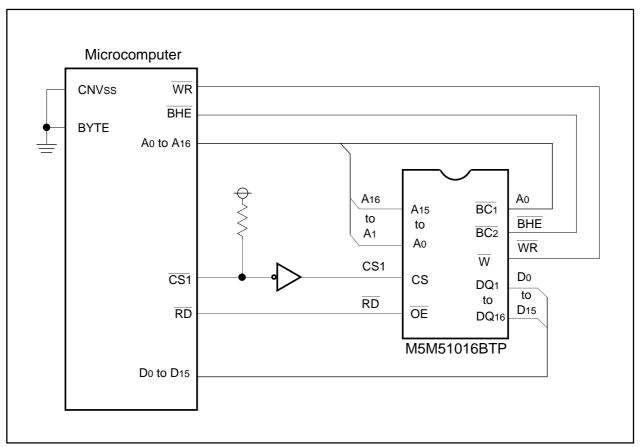

| 4.3 Connection Examples                                                            | 26 |

|------------------------------------------------------------------------------------|----|

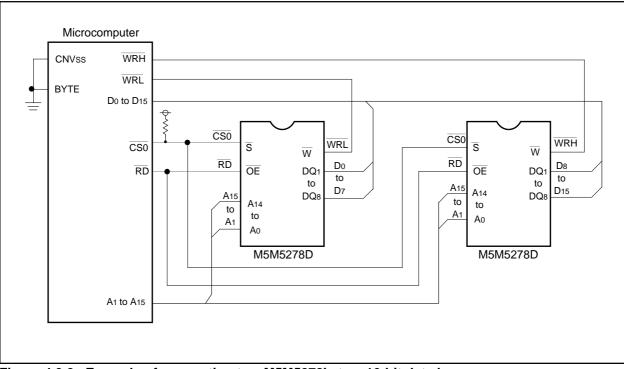

| 4.3.1 16-bit Memory to 16-bit Width Data Bus Connection Example 2-22               | 26 |

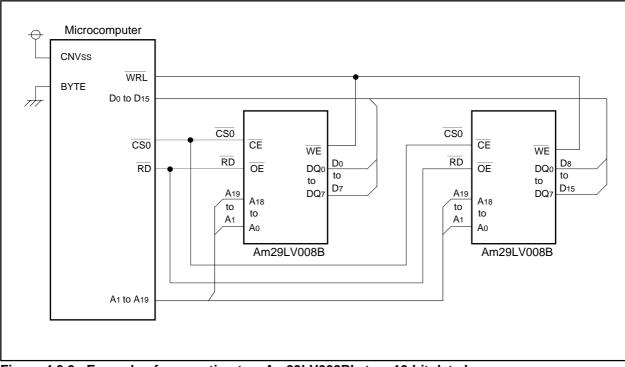

| 4.3.2 8-bit Memory to 16-bit Width Data Bus Connection Example 2-22                | 27 |

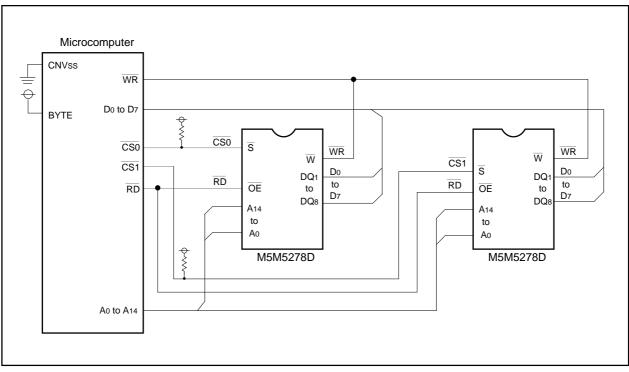

| 4.3.3 8-bit Memory to 8-bit Width Data Bus Connection Example 2-22                 | 29 |

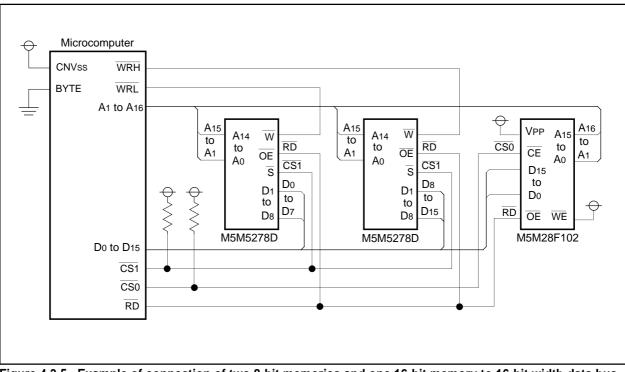

| 4.3.4 Two 8-bit and 16-Bit Memory to 16-Bit Width Data Bus Connection Example 2-23 | 30 |

| 4.3.5 Chip Selects and Address Bus 2-23                                            | 31 |

| 4.4 Connectable Memories                                                           | 32 |

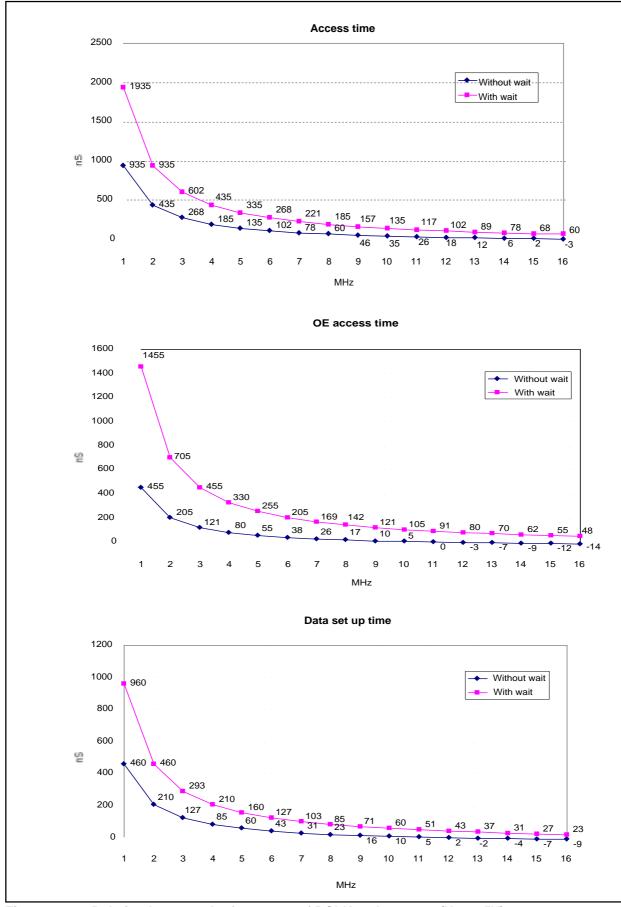

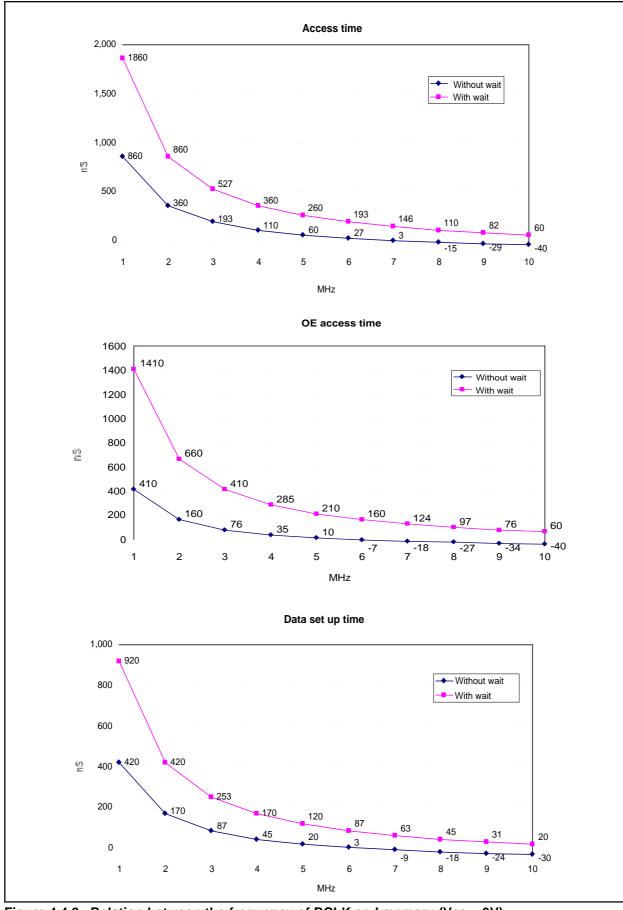

| 4.4.1 Operation Frequency and Access Time 2-23                                     | 32 |

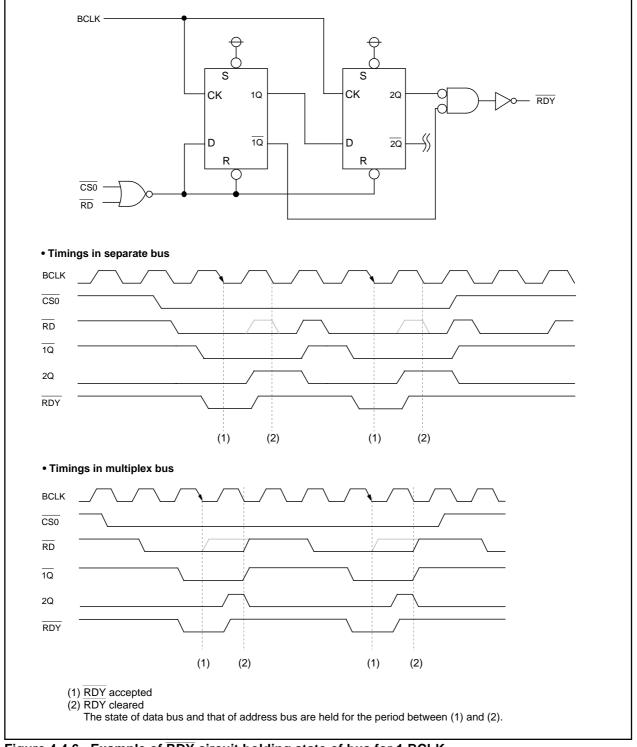

| 4.4.2 Connecting Low-Speed Memory 2-23                                             | 36 |

| 4.4.3 Connectable Memories 2-24                                                    | 40 |

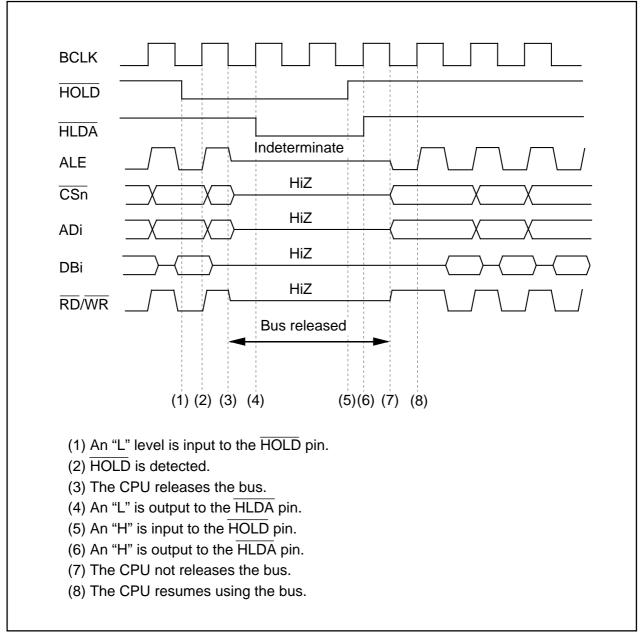

| 4.5 Releasing an External Bus (HOLD input and HLDA output) 2-24                    | 41 |

| 4.6 Precautions for External Bus                                                   | 42 |

## Chapter 5 External ROM Version \_\_\_\_\_

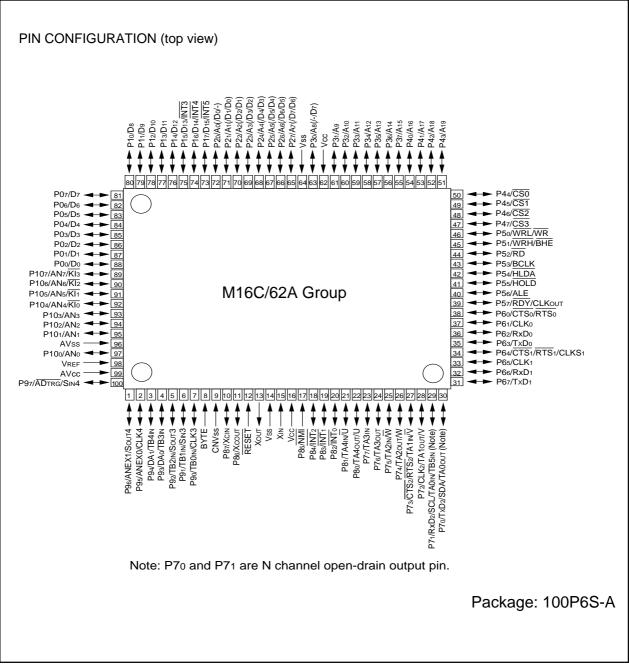

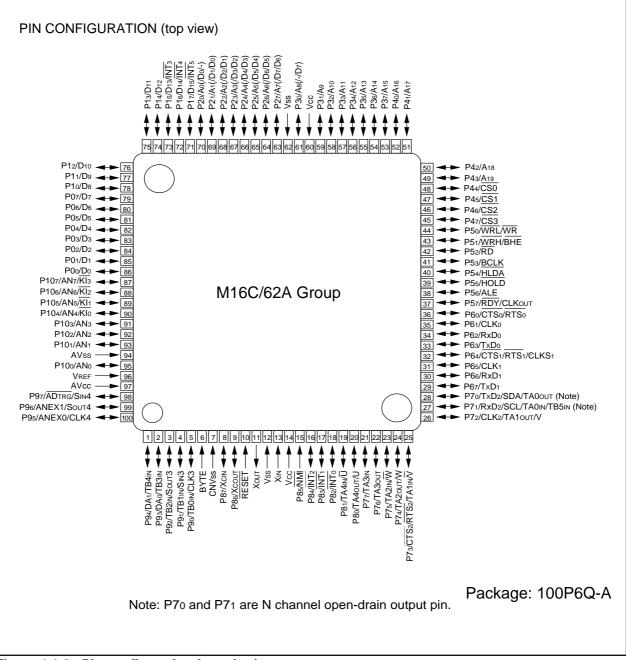

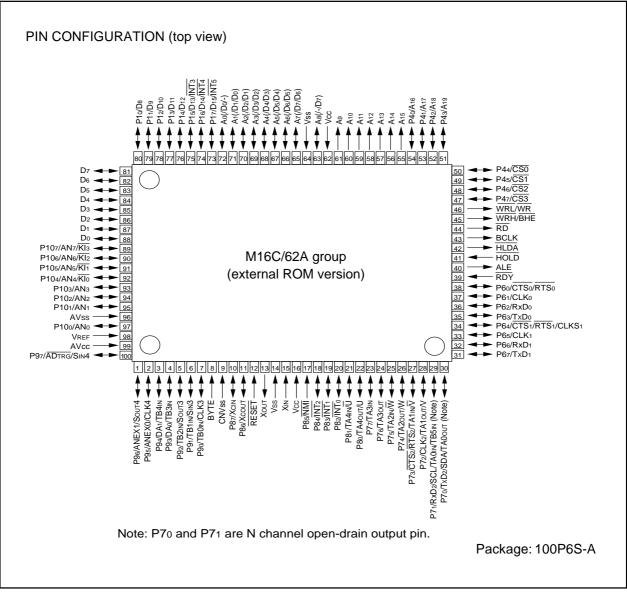

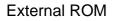

| 5.1 Pin Configuration | 2-245 |

|-----------------------|-------|

| 5.2 Pin Description   | 2-247 |

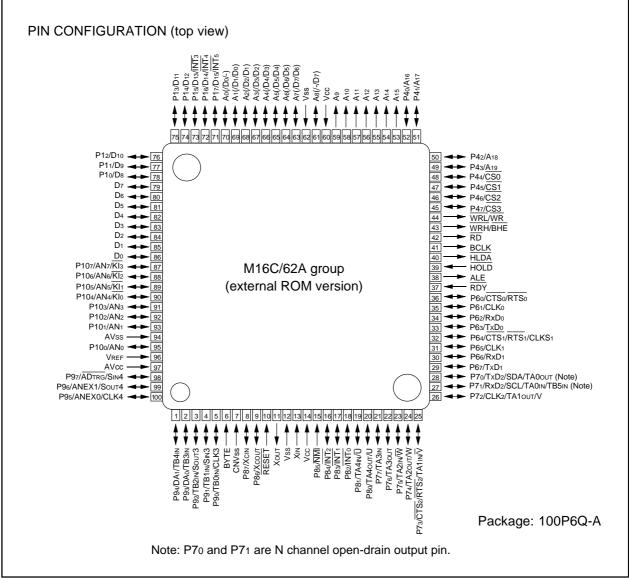

| 5.3 Memory Map        | 2-249 |

| 5.4 Processor Mode    | 2-253 |

## Table of Contents Classified by Function

| Protection                                                                                         | 1-45   |

|----------------------------------------------------------------------------------------------------|--------|

| 2.1.1 Overview of the protect usage                                                                | 2-2    |

| 2.1.2 Protect Operation                                                                            | 2-4    |

| 2.1.3 Precaution for Protect                                                                       | 2-5    |

| Timer A                                                                                            | 1-80   |

| 2.2.1 Overview of the timer A usage                                                                | 2-6    |

| 2.2.2 Operation of Timer A (timer mode)                                                            | 2-12   |

| 2.2.3 Operation of Timer A (timer mode, gate function selected)                                    | 2-14   |

| 2.2.4 Operation of Timer A (timer mode, pulse output function selected)                            | 2-16   |

| 2.2.5 Operation of Timer A (event counter mode, reload type selected)                              | 2-18   |

| 2.2.6 Operation of Timer A (event counter mode, free run type selected)                            | 2-20   |

| 2.2.7 Operation of timer A (2-phase pulse signal process in event counter mode, norm lected)       |        |

| 2.2.8 Operation of timer A (2-phase pulse signal process in event counter mode, multiply selected) | -      |

| 2.2.9 Operation of Timer A (one-shot timer mode)                                                   | 2-26   |

| 2.2.10 Operation of Timer A (one-shot timer mode, external trigger selected)                       | 2-28   |

| 2.2.11 Operation of Timer A (pulse width modulation mode, 16-bit PWM mode selected                 | ) 2-30 |

| 2.2.12 Operation of Timer A (pulse width modulation mode, 8-bit PWM mode selected)                 | 2-32   |

| 2.2.13 Precautions for Timer A (timer mode)                                                        | 2-34   |

| 2.2.14 Precautions for Timer A (event counter mode)                                                | 2-35   |

| 2.2.15 Precautions for Timer A (one-shot timer mode)                                               | 2-36   |

| 2.2.16 Precautions for Timer A (pulse width modulation mode)                                       | 2-37   |

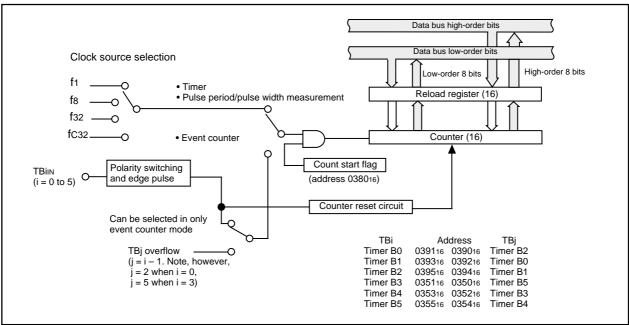

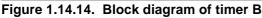

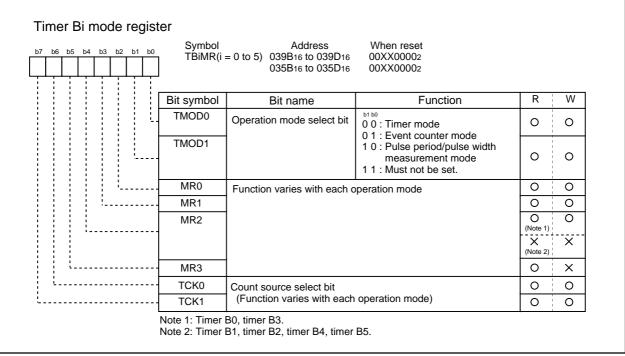

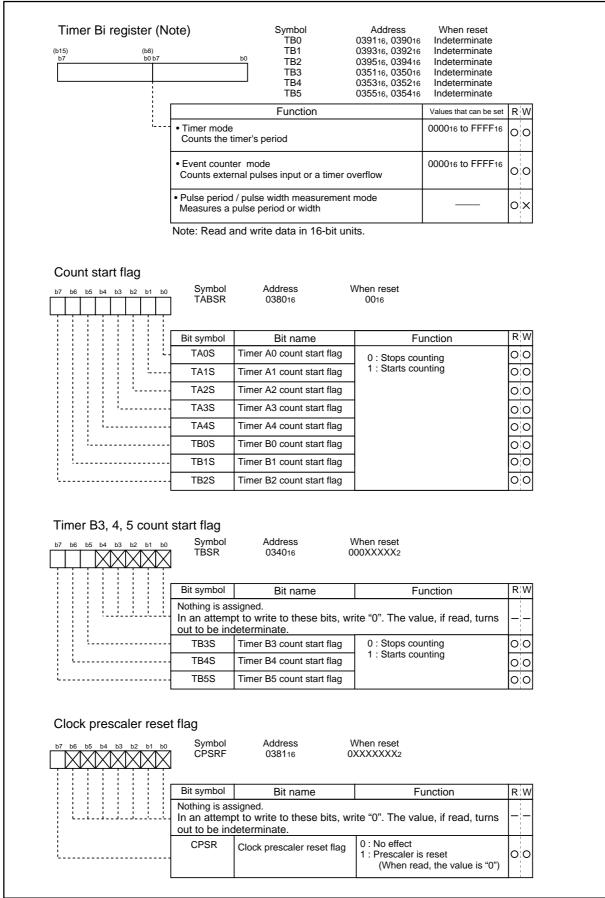

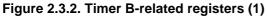

| Timer B                                                                                            | 1-90   |

| 2.3.1 Overview of the timer B usage                                                                | 2-38   |

| 2.3.2 Operation of Timer B (timer mode)                                                            | 2-42   |

| 2.3.3 Operation of Timer B (event counter mode)                                                    | 2-44   |

| 2.3.4 Operation of Timer B (pulse period measurement mode)                                         | 2-46   |

| 2.3.5 Operation of Timer B (pulse width measurement mode)                                          | 2-48   |

| 2.3.6 Precautions for Timer B (timer mode, event counter mode)                                     | 2-50   |

| 2.3.7 Precautions for Timer B (pulse period/pulse width measurement mode)                          | 2-51   |

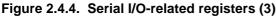

| Serial I/O                                                                                                                           | 1-108        |

|--------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 2.4.1 Overview of the clock-synchronous serial I/O usage                                                                             | 2-52         |

| 2.4.2 Operation of Serial I/O (transmission in clock-synchronous serial I/O mode)                                                    | 2-60         |

| 2.4.3 Operation of the Serial I/O (transmission in clock-synchronous serial I/O mode, t output from multiple pins function selected) |              |

| 2.4.4 Operation of Serial I/O (reception in clock-synchronous serial I/O mode)                                                       | 2-68         |

| 2.4.5 Precautions for Serial I/O (in clock-synchronous serial I/O)                                                                   | 2-72         |

| 2.5.1 Overview of the clock-asynchronous serial I/O usage                                                                            | 2-74         |

| 2.5.2 Operation of Serial I/O (transmission in UART mode)                                                                            | 2-84         |

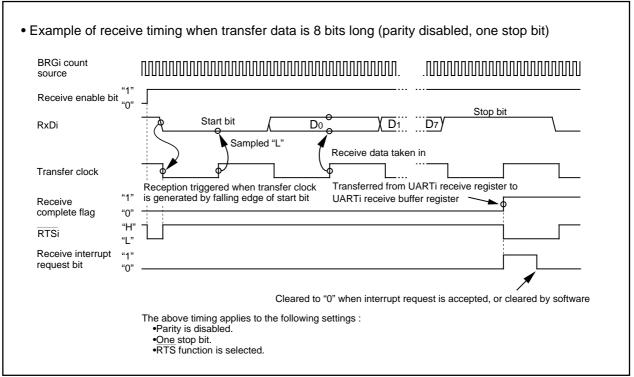

| 2.5.3 Operation of Serial I/O (reception in UART mode)                                                                               | 2-88         |

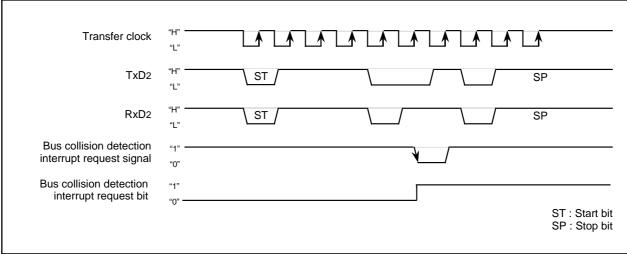

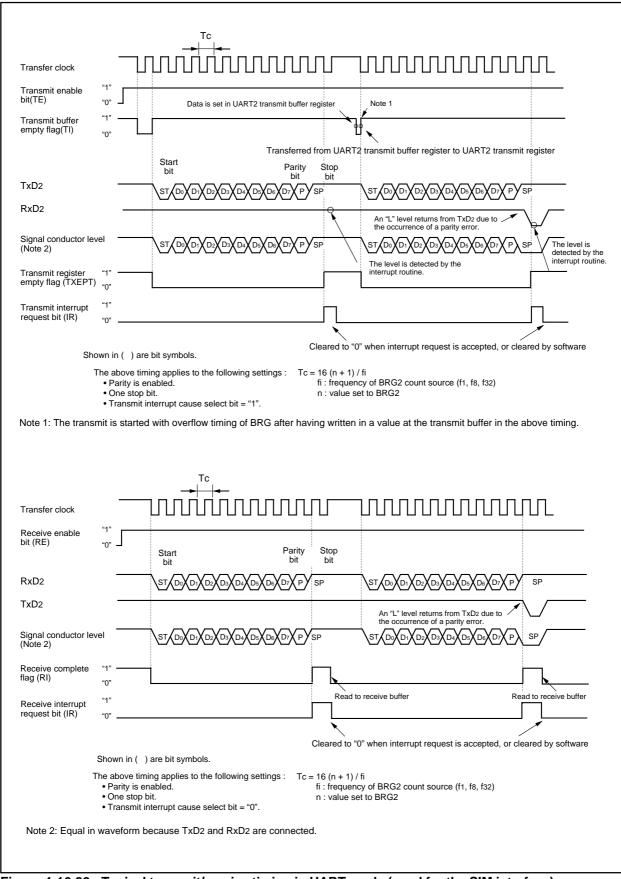

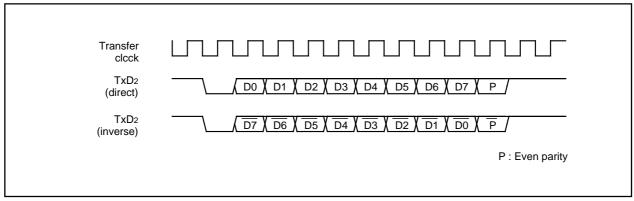

| 2.5.4 Operation of Serial I/O (transmission used for SIM interface)                                                                  | 2-92         |

| 2.5.5 Operation of Serial I/O (reception used for SIM interface)                                                                     | 2-96         |

| 2.5.6 Clock Signals in used for the SIM Interface                                                                                    | 2-100        |

| 2.5.7 Error-permitted range range of transfer baud                                                                                   | 2-104        |

| 2.6.1 Overview of the SI/O3,4 usage                                                                                                  | 2-106        |

| 2.6.2 Operation of SI/O3,4                                                                                                           | 2-108        |

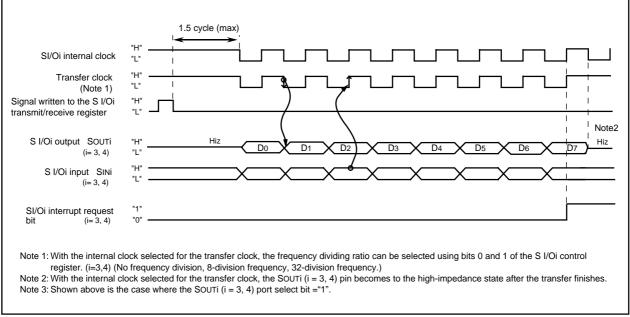

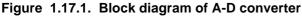

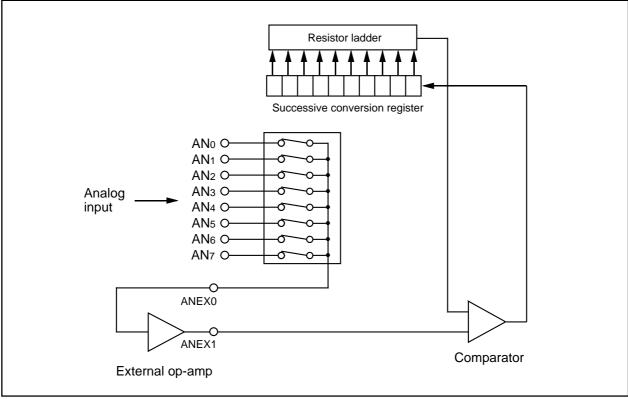

| A-D Converter                                                                                                                        | 1-149        |

| 2.7.1 Overview of the A-D converter usage                                                                                            | 2-110        |

| 2.7.2 Operation of A-D converter (one-shot mode)                                                                                     | 2-116        |

| 2.7.3 Operation of A-D Converter (in one-shot mode, an external trigger selected)                                                    | 2-118        |

| 2.7.4 Operation of A-D Converter (in one-shot mode, expanded analog input pin select                                                 | ed) 2-120    |

| 2.7.5 Operation of A-D Converter (in one-shot mode, external op-amp connection mod                                                   | e selected). |

|                                                                                                                                      | 2-122        |

| 2.7.6 Operation of A-D Converter (in repeat mode)                                                                                    | 2-124        |

| 2.7.7 Operation of A-D Converter (in single sweep mode)                                                                              | 2-126        |

| 2.7.8 Operation of A-D Converter (in repeat sweep mode 0)                                                                            | 2-128        |

| 2.7.9 Operation of A-D Converter (in repeat sweep mode 1)                                                                            | 2-130        |

| 2.7.10 Precautions for A-D Converter                                                                                                 | 2-132        |

| 2.7.11 Method of A-D Conversion (10-bit mode)                                                                                        | 2-133        |

| 2.7.12 Method of A-D Conversion (8-bit mode)                                                                                         | 2-135        |

| 2.7.13 Absolute Accuracy and Differential Non-Linearity Error                                                                        | 2-137        |

| 2.7.14 Internal Equivalent Circuit of Analog Input                                                                                   | 2-139        |

| 2.7.15 Sensor's Output Impedance under A-D Conversion                                                                                | 2-140        |

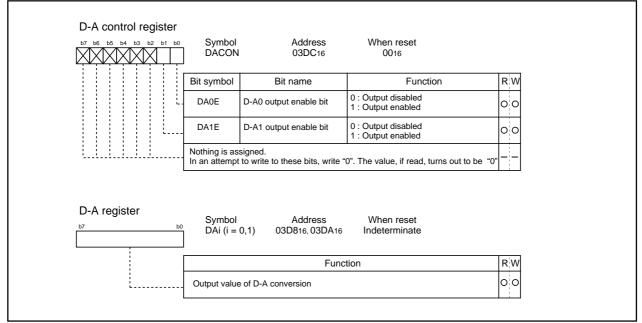

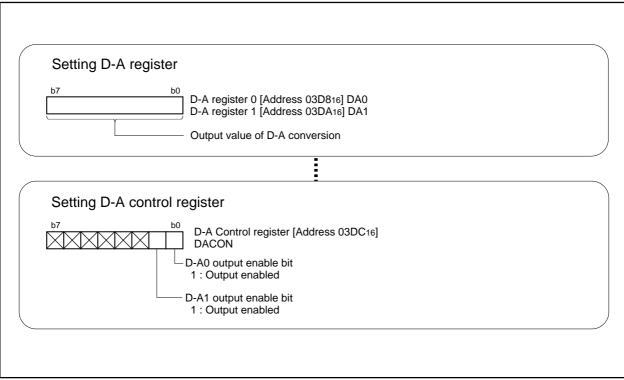

| D-A Converter                                                                                                                        | 1-159        |

| 2.8.1 Overview of the D-A converter usage                                                                                            | 2-142        |

| 2.8.2 D-A Converter Operation                        | 2-143 |

|------------------------------------------------------|-------|

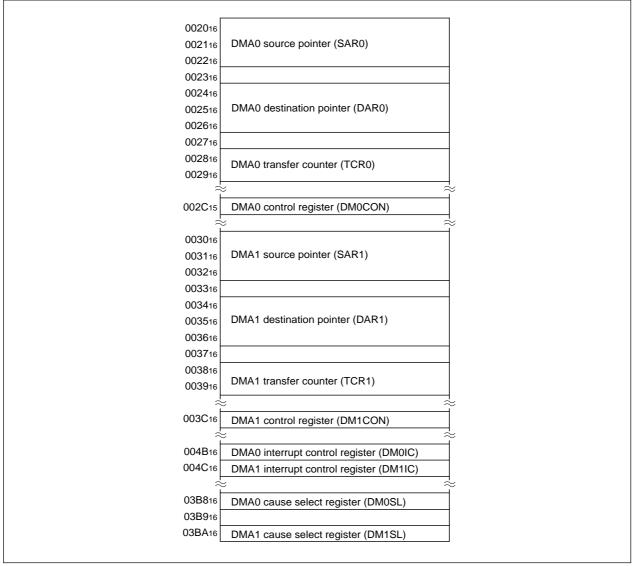

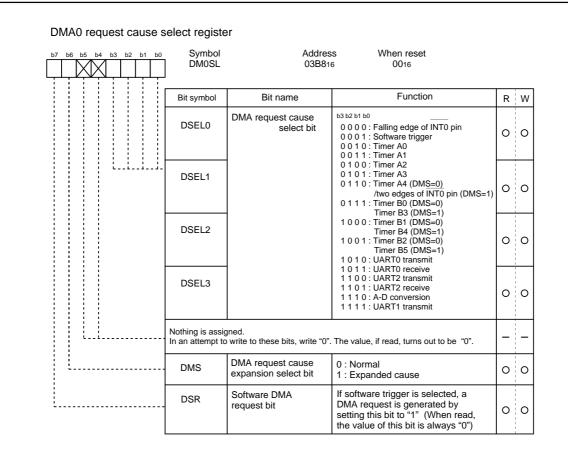

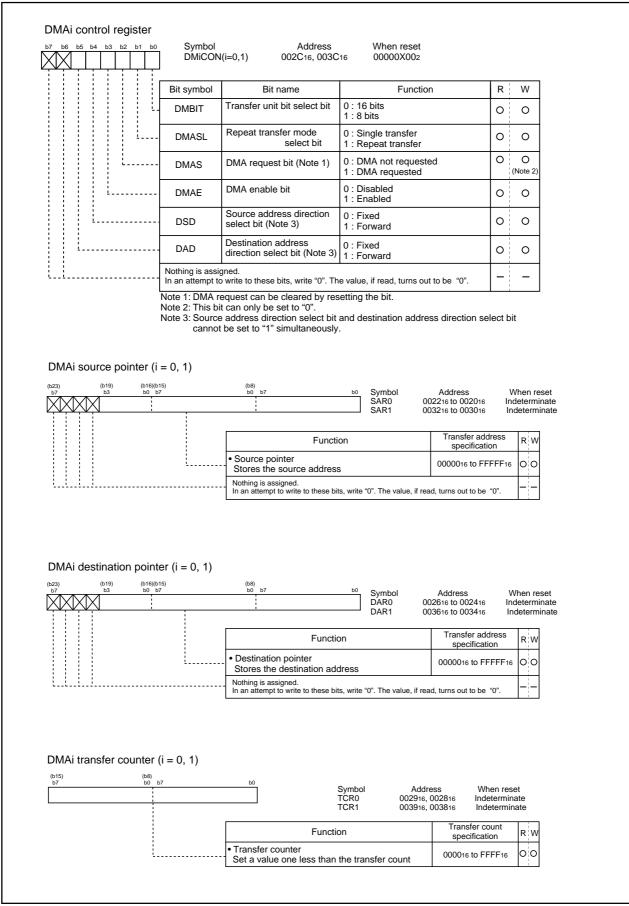

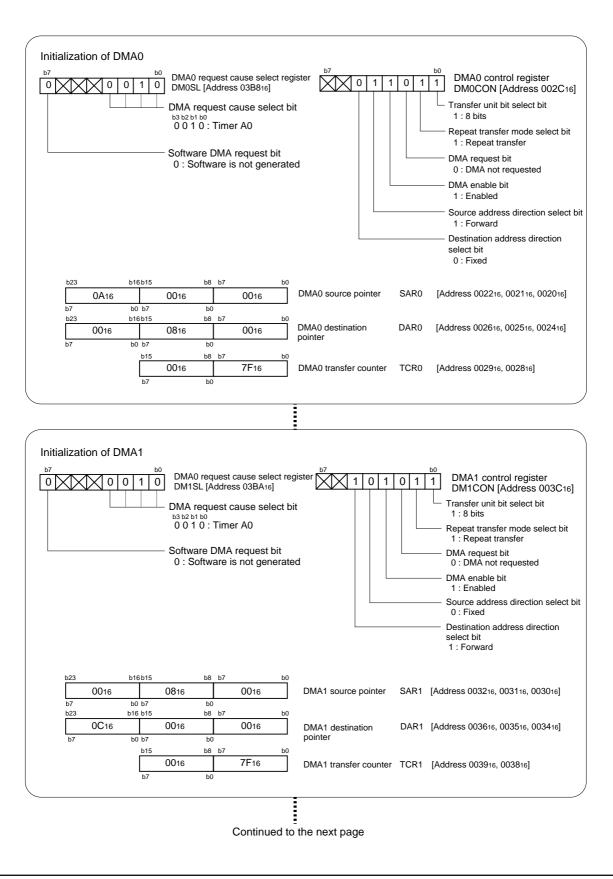

| DMAC                                                 | 1-68  |

| 2.9.1 Overview of the DMAC usage                     | 2-144 |

| 2.9.2 Operation of DMAC (one-shot transfer mode)     | 2-148 |

| 2.9.3 Operation of DMAC (repeated transfer mode)     | 2-150 |

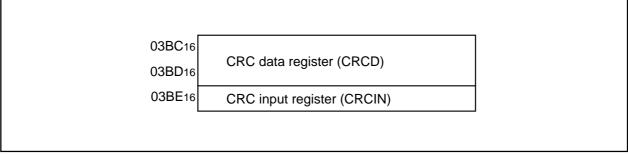

| CRC Calculation Circuit                              | 1-161 |

| 2.10.1 Overview of the CRC calculation circuit usage | 2-152 |

| 2.10.2 Operation of CRC Calculation Circuit          | 2-153 |

| Watchdog Timer                                       | 1-66  |

| 2.11.1 Overview of the watchdog timer usage          | 2-154 |

| 2.11.2 Operation of Watchdog Timer                   | 2-156 |

| Overview of Interrupt                                | 1-46  |

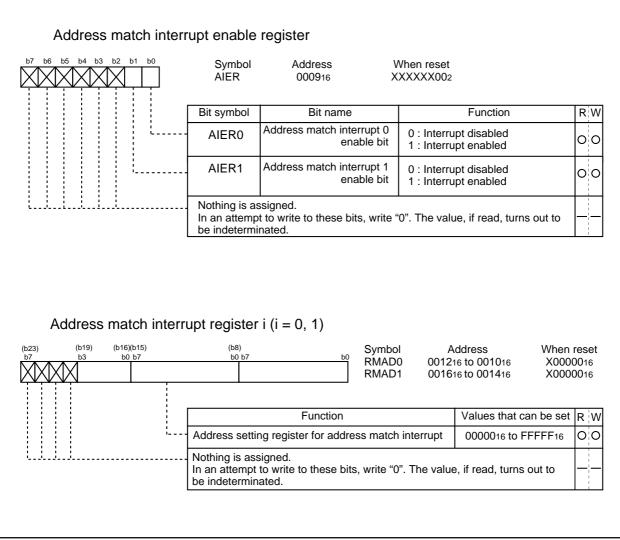

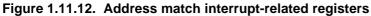

| 2.12.1 Overview of the address match interrupt usage | 2-158 |

| 2.12.2 Operation of Address Match Interrupt          | 2-160 |

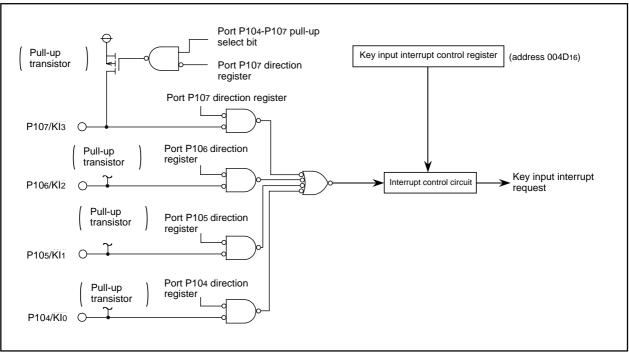

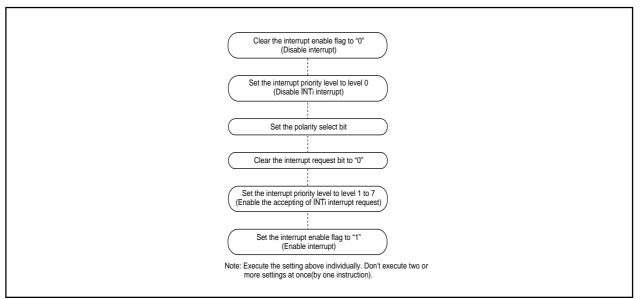

| 2.13.1 Overview of the key-input interrupt usage     | 2-162 |

| 2.13.2 Operation of Key-Input Interrupt              | 2-164 |

| 2.14.1 Overview of the Multiple interrupts usage     | 2-166 |

| 2.14.2 Multiple Interrupts operation                 | 2-171 |

| Power Control                                        | 1-43  |

| 2.15.1 Overview of the power control usage           | 2-173 |

| 2.15.2 Stop Mode Set-Up                              | 2-178 |

| 2.15.3 Wait Mode Set-Up                              | 2-179 |

| 2.15.4 Precautions in Power Control                  | 2-180 |

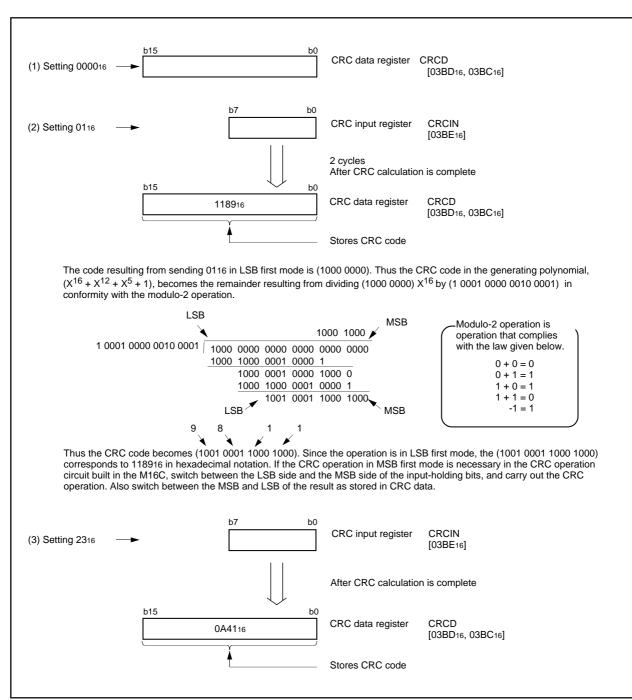

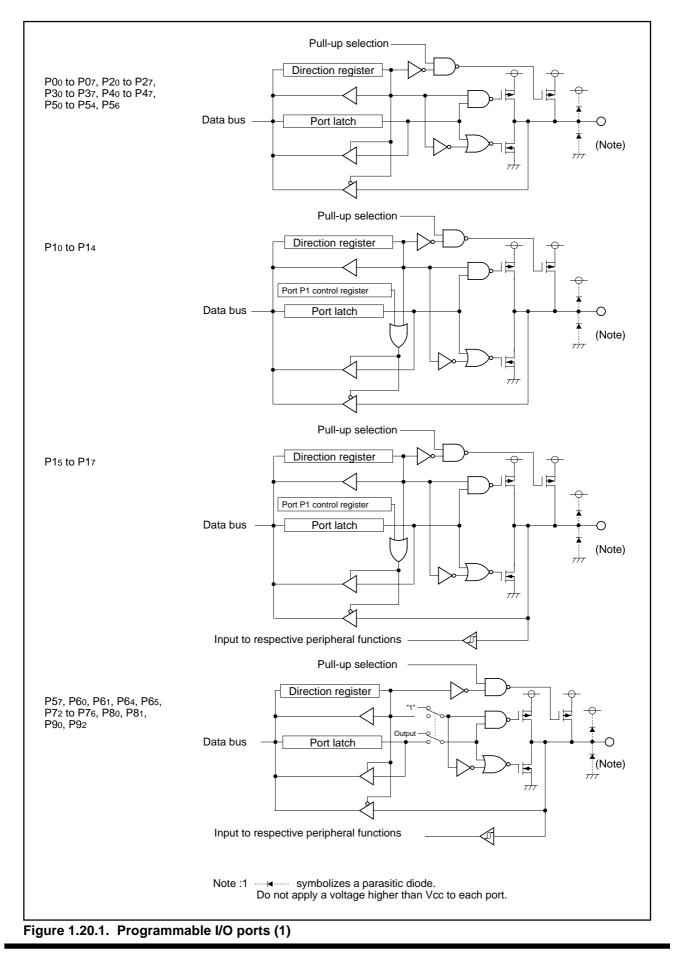

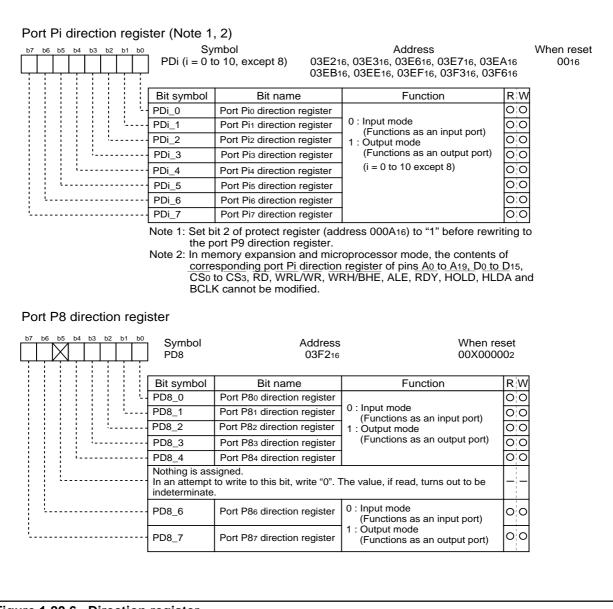

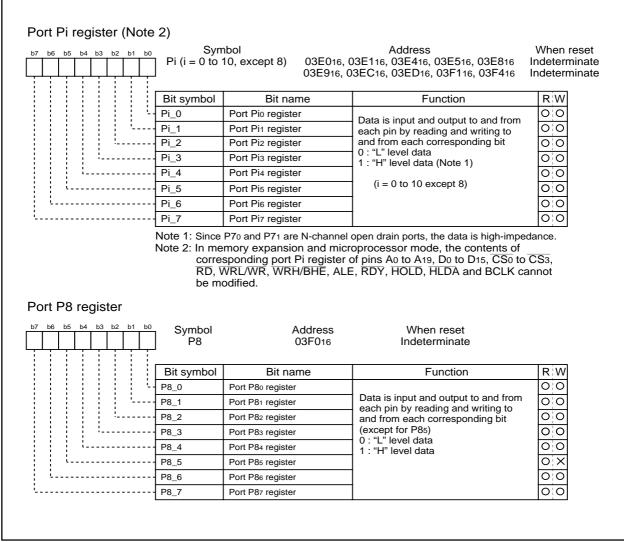

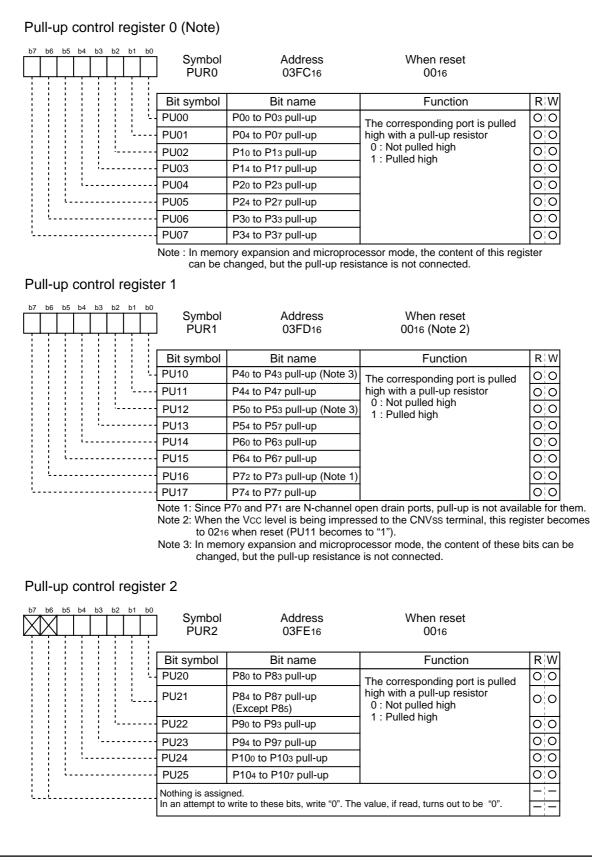

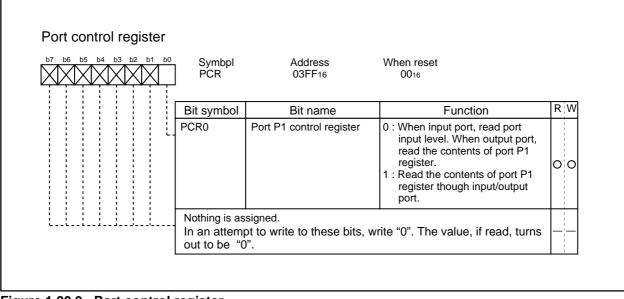

| Programmable I/O Ports                               | 1-163 |

| 2.16.1 Overview of the programmable I/O ports usage  | 2-181 |

### Quick Reference to Pages Classified by Address

| Page     | ss Register                                    |

|----------|------------------------------------------------|

|          |                                                |

|          |                                                |

|          |                                                |

|          |                                                |

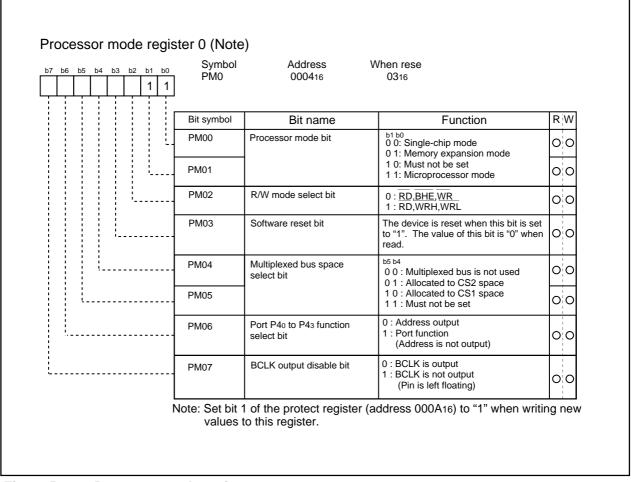

| 1-23     | Processor mode register 0 (PM0)                |

| 1-23     | Processor mode register 1 (PM1)                |

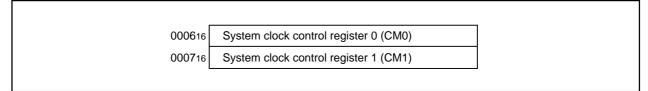

| 1 20     | System clock control register 0 (CM0)          |

| 1-39     | System clock control register 1 (CM1)          |

| 1-29     | Chip select control register (CSR)             |

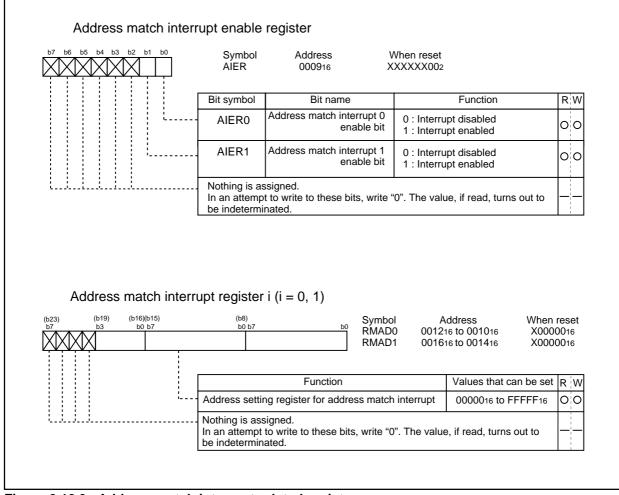

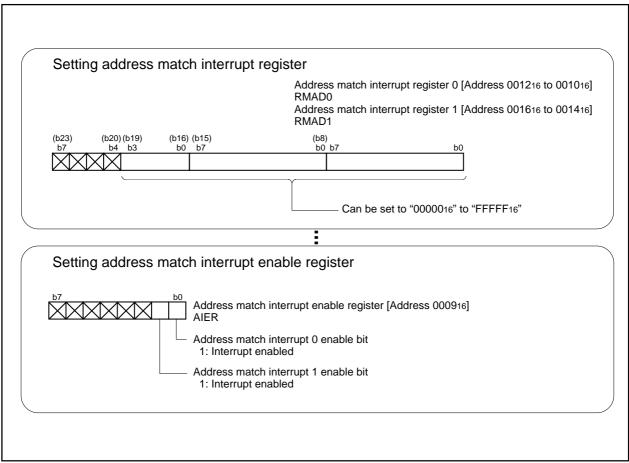

| 1-63     | Address match interrupt enable register (AIER) |

| 1-38     | Protect register (PRCR)                        |

|          |                                                |

|          |                                                |

|          |                                                |

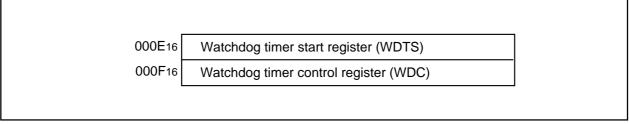

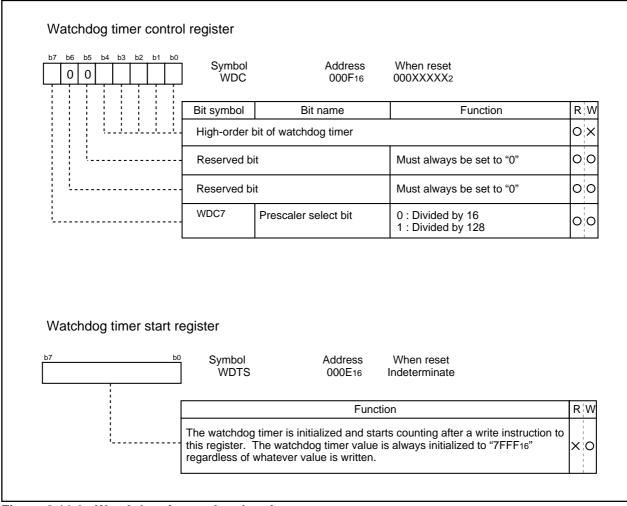

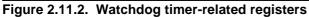

| 1 67     | Watchdog timer start register (WDTS)           |

| 1-67     | Watchdog timer control register (WDC)          |

|          | <u>_</u>                                       |

| 1-63     | Address match interrupt register 0 (RMAD0)     |

|          |                                                |

|          |                                                |

| 1        |                                                |

| 1-63     | Address match interrupt register 1 (RMAD1)     |

|          |                                                |

| <u> </u> |                                                |

| 1        |                                                |

| 1        |                                                |

| 1        |                                                |

| 1        |                                                |

| 1        |                                                |

|          |                                                |

|          |                                                |

|          |                                                |

| -        |                                                |

| 1-72     | DMA0 source pointer (SAR0)                     |

| 1-72     | DMA0 source pointer (SAR0)                     |

|          |                                                |

|          |                                                |

| 4 70     | DMAQ destination resiston (DADQ)               |

| 1-72     | DMA0 destination pointer (DAR0)                |

|          |                                                |

|          |                                                |

| 1-72     | DMA0 transfer counter (TCR0)                   |

|          |                                                |

| 4        |                                                |

| L        |                                                |

| 1-71     | DMA0 control register (DM0CON)                 |

| 1        |                                                |

|          |                                                |

|          |                                                |

|          |                                                |

| 1-72     | DMA1 source pointer (SAR1)                     |

|          |                                                |

|          |                                                |

|          |                                                |

| 1-72     | DMA1 destination pointer (DAR1)                |

|          |                                                |

|          |                                                |

| 4 70     |                                                |

| 1-72     | DMA1 transfer counter (TCR1)                   |

| 1        |                                                |

| 1        |                                                |

| 1        |                                                |

| 1-71     | DMA1 control register (DM1CON)                 |

| 1-71     | DMA1 control register (DM1CON)                 |

| 1-71     | DMA1 control register (DM1CON)                 |

| Addres           | ss Register                                                                                | Page |

|------------------|--------------------------------------------------------------------------------------------|------|

| 004016           |                                                                                            |      |

| 004116           |                                                                                            |      |

| 004216           |                                                                                            |      |

| 004316           | INT3 interrupt control register (INT3IC)                                                   |      |

| 004416<br>004516 | Timer B5 interrupt control register (TB5IC)                                                |      |

| 004518           | Timer B4 interrupt control register (TB4IC)                                                |      |

| 004016           | Timer B3 interrupt control register (TB3IC)                                                |      |

| 004816           | SI/O4 interrupt control register (S4IC)                                                    |      |

|                  | INT5 interrupt control register (INT5IC)                                                   |      |

| 004916           | SI/O3 interrupt control register (S3IC)                                                    |      |

|                  | INT4 interrupt control register (INT4IC)                                                   |      |

| 004A16           | Bus collision detection interrupt control register (BCNIC)                                 |      |

| 004B16           | DMA0 interrupt control register (DM0IC)                                                    |      |

| 004C16           | DMA1 interrupt control register (DM1IC)<br>Key input interrupt control register (KUPIC)    |      |

| 004D16<br>004E16 | A-D conversion interrupt control register (ADIC)                                           |      |

| 004E16           | UART2 transmit interrupt control register (S2TIC)                                          | 4 50 |

| 005016           | UART2 receive interrupt control register (S2RIC)                                           | 1-52 |

| 005116           | UART0 transmit interrupt control register (S0TIC)                                          |      |

| 005216           | UART0 receive interrupt control register (S0RIC)                                           |      |

| 005316           | UART1 transmit interrupt control register (S1TIC)                                          |      |

| 005416           | UART1 receive interrupt control register (S1RIC)                                           |      |

| 005516           | Timer A0 interrupt control register (TA0IC)                                                |      |

| 005616           | Timer A1 interrupt control register (TA1IC)<br>Timer A2 interrupt control register (TA2IC) |      |

| 005716           | Timer A3 interrupt control register (TA3IC)                                                |      |

| 005816<br>005916 | Timer A4 interrupt control register (TA4IC)                                                |      |

| 005916<br>005A16 | Timer B0 interrupt control register (TB0IC)                                                |      |

| 005B16           | Timer B1 interrupt control register (TB1IC)                                                |      |

| 005C16           | Timer B2 interrupt control register (TB2IC)                                                |      |

| 005D16           | INT0 interrupt control register (INT0IC)                                                   |      |

| 005E16           | INT1 interrupt control register (INT1IC)                                                   |      |

| 005F16           | INT2 interrupt control register (INT2IC)                                                   |      |

| 006016           |                                                                                            |      |

| 006116           |                                                                                            |      |

| 006216<br>006316 |                                                                                            |      |

| 006316           |                                                                                            |      |

| 006516           |                                                                                            |      |

|                  |                                                                                            |      |

|                  |                                                                                            |      |

| $\widehat{}$     | × A                                                                                        | Ĕ    |

|                  |                                                                                            |      |

| 032A16           |                                                                                            |      |

| 032B16           |                                                                                            |      |

| 032C16<br>032D16 |                                                                                            |      |

| 032D16<br>032E16 |                                                                                            |      |

| 032E16           |                                                                                            |      |

| 033016           |                                                                                            |      |

| 033116           |                                                                                            |      |

| 033216           |                                                                                            |      |

| 033316           |                                                                                            |      |

| 033416           |                                                                                            |      |

| 033516           |                                                                                            |      |

| 033616           |                                                                                            |      |

| 033716           |                                                                                            |      |

| 033816           |                                                                                            |      |

| 033916<br>033A16 |                                                                                            |      |

| 033B16           |                                                                                            |      |

| 033C16           |                                                                                            |      |

| 033D16           |                                                                                            |      |

| 033E16           |                                                                                            |      |

| 033F16           |                                                                                            |      |

| L                |                                                                                            |      |

Note : Locations in the SFR area where nothing is allocated are reserved areas. Do not access these areas for read or write.

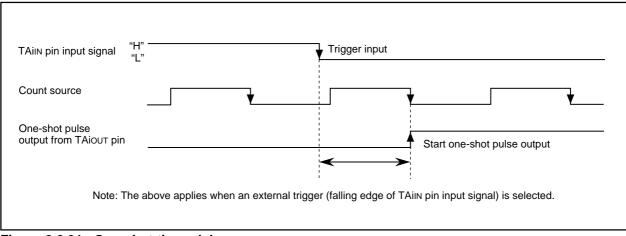

#### Quick Reference to Pages Classified by Address

| Addre                                                              | ss Register                                                                                                                                                                  | Page                    |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 034016                                                             | Timer B3, 4, 5 count start flag (TBSR)                                                                                                                                       | 1-91                    |

| 034116                                                             |                                                                                                                                                                              |                         |

| 034216                                                             | Timer A1-1 register (TA11)                                                                                                                                                   |                         |

| 034316                                                             |                                                                                                                                                                              | -                       |

| 034416                                                             | Timer A2-1 register (TA21)                                                                                                                                                   | 1-98                    |

| 034516                                                             |                                                                                                                                                                              |                         |

| 034616                                                             | Timer A4-1 register (TA41)                                                                                                                                                   |                         |

| 034716<br>034816                                                   | • • •                                                                                                                                                                        |                         |

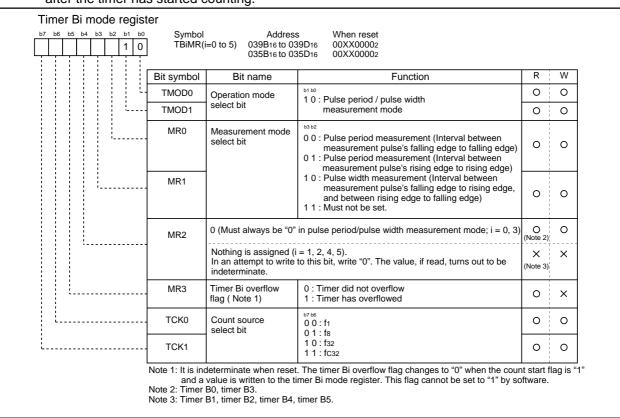

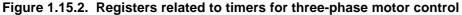

| )34816<br>)34916                                                   | Three-phase PWM control register 0(INVC0)<br>Three-phase PWM control register 1(INVC1)                                                                                       | 1-96                    |

| )34916<br>)34A16                                                   | Three-phase output buffer register 0(IDB0)                                                                                                                                   |                         |

| 34B16                                                              | Three-phase output buffer register 1(IDB1)                                                                                                                                   | -                       |

| 34C16                                                              | Dead time timer(DTT)                                                                                                                                                         | 1-97                    |

| 34D16                                                              | Timer B2 interrupt occurrence frequency set counter(ICTB2)                                                                                                                   |                         |

| 34E16                                                              |                                                                                                                                                                              |                         |

| 34F16                                                              |                                                                                                                                                                              |                         |

| 35016                                                              | Timer P2 register (TP2)                                                                                                                                                      |                         |

| 35116                                                              | Timer B3 register (TB3)                                                                                                                                                      |                         |

| 35216                                                              | Timor P4 register (TP4)                                                                                                                                                      | 1-91                    |

| 35316                                                              | Timer B4 register (TB4)                                                                                                                                                      |                         |

| 35416                                                              | Timer B5 register (TB5)                                                                                                                                                      |                         |

| 35516                                                              |                                                                                                                                                                              |                         |

| 35616                                                              |                                                                                                                                                                              |                         |

| 35716                                                              |                                                                                                                                                                              |                         |

| 035816                                                             |                                                                                                                                                                              | -                       |

| 035916                                                             |                                                                                                                                                                              |                         |

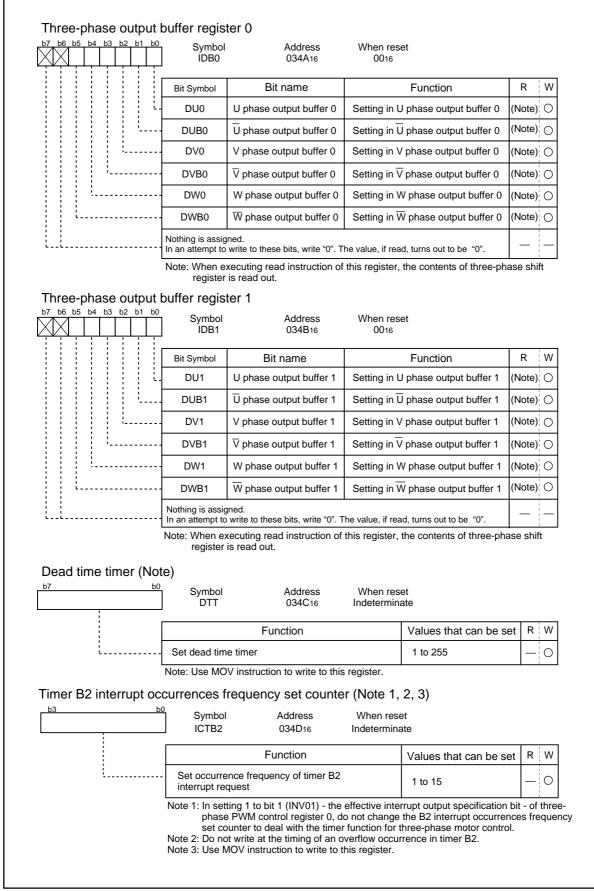

| 035A16<br>035B16                                                   | Timer B3 mode register (TB3MR)                                                                                                                                               |                         |

| 035C16                                                             | Timer B4 mode register (TB4MR)                                                                                                                                               | 1-90                    |

| 035D16                                                             | Timer B5 mode register (TB5MR)                                                                                                                                               | 1-30                    |

| 35E16                                                              |                                                                                                                                                                              |                         |

| )35F16                                                             | Interrupt request cause select register (IFSR)                                                                                                                               | 1-61                    |

| 36016                                                              | SI/O3 transmit/receive register (S3TRR)                                                                                                                                      |                         |

| 36116                                                              |                                                                                                                                                                              |                         |

| 036216                                                             | SI/O3 control register (S3C)                                                                                                                                                 |                         |

| 036316                                                             | SI/O3 bit rate generator (S3BRG)                                                                                                                                             | 1-146                   |

| 36416                                                              | SI/O4 transmit/receive register (S4TRR)                                                                                                                                      | 1-140                   |

| 036516                                                             |                                                                                                                                                                              |                         |

| 36616                                                              | SI/O4 control register (S4C)                                                                                                                                                 |                         |

| 36716                                                              | SI/O4 bit rate generator (S4BRG)                                                                                                                                             |                         |

| 36816                                                              |                                                                                                                                                                              |                         |

| 36916                                                              |                                                                                                                                                                              | -                       |

| 36A16                                                              |                                                                                                                                                                              |                         |

| 36B16<br>36C16                                                     |                                                                                                                                                                              | 1                       |

| 36D16                                                              |                                                                                                                                                                              | 1                       |

| 36E16                                                              |                                                                                                                                                                              | 1                       |

| 36F16                                                              |                                                                                                                                                                              | 1                       |

| 37016                                                              |                                                                                                                                                                              | 1                       |

| 37116                                                              |                                                                                                                                                                              | ]                       |

| 37216                                                              |                                                                                                                                                                              |                         |

| 37316                                                              |                                                                                                                                                                              | _                       |

| 37416                                                              |                                                                                                                                                                              |                         |

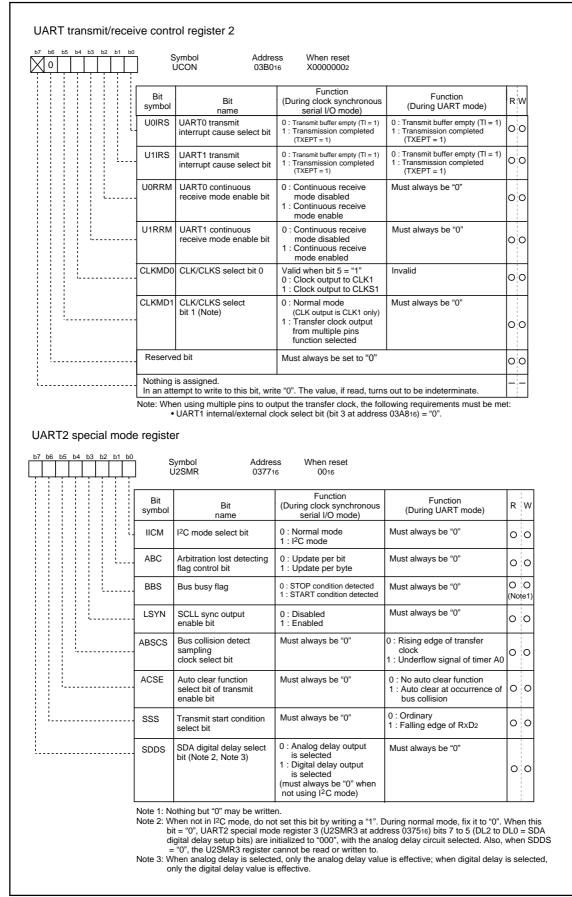

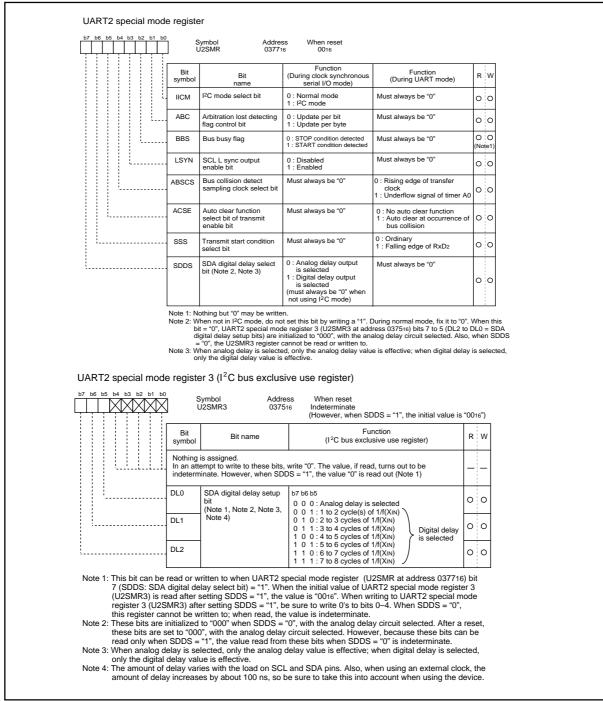

| 37516                                                              | UART2 special mode register 3 (U2SMR3)                                                                                                                                       | 1-137                   |

| t                                                                  | UART2 special mode register 2 (U2SMR2)                                                                                                                                       | 1-141                   |

| 37616                                                              |                                                                                                                                                                              | 1-137                   |

| 137616<br>137716                                                   | UART2 special mode register (U2SMR)                                                                                                                                          |                         |

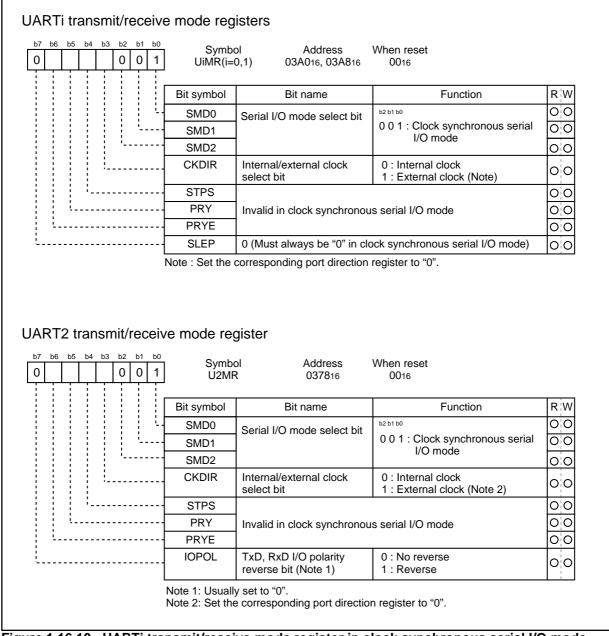

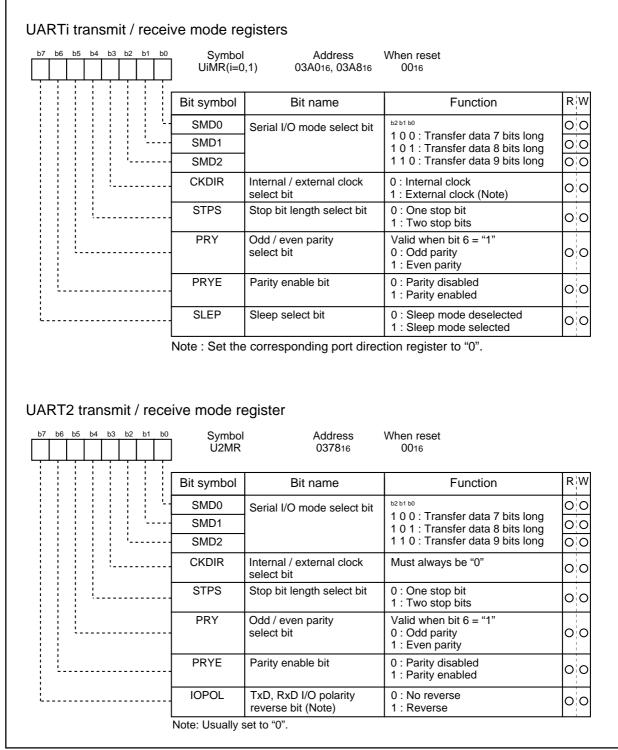

| )37616<br>)37716<br>)37816                                         | UART2 transmit/receive mode register (U2MR)                                                                                                                                  | 1-113                   |

| )37616<br>)37716<br>)37816<br>)37916                               |                                                                                                                                                                              | 1-113                   |

| 037616<br>037716<br>037816<br>037916<br>037A16                     | UART2 transmit/receive mode register (U2MR)                                                                                                                                  |                         |

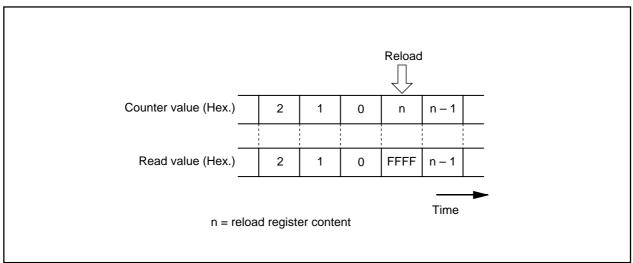

| )37616<br>)37716<br>)37816<br>)37916<br>)37A16<br>)37B16           | UART2 transmit/receive mode register (U2MR)<br>UART2 bit rate generator (U2BRG)<br>UART2 transmit buffer register (U2TB)                                                     | 1-113<br>1-112          |

| )37616<br>)37716<br>)37816<br>)37916<br>)37A16<br>)37B16<br>)37C16 | UART2 transmit/receive mode register (U2MR)<br>UART2 bit rate generator (U2BRG)<br>UART2 transmit buffer register (U2TB)<br>UART2 transmit/receive control register 0 (U2C0) | 1-113<br>1-112<br>1-114 |

| )37616<br>)37716<br>)37816<br>)37916                               | UART2 transmit/receive mode register (U2MR)<br>UART2 bit rate generator (U2BRG)<br>UART2 transmit buffer register (U2TB)                                                     | 1-113<br>1-112          |

| Addre            | ss Register                                                                                        | Page  |

|------------------|----------------------------------------------------------------------------------------------------|-------|

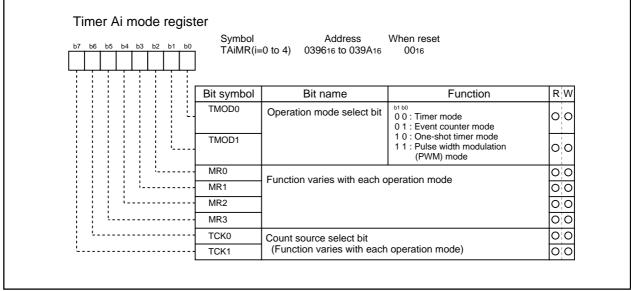

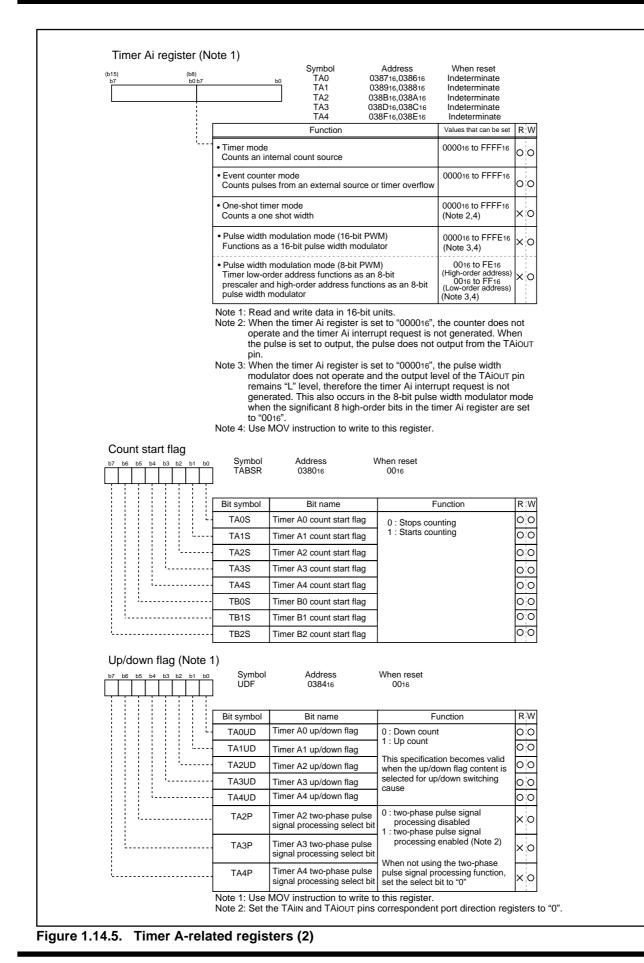

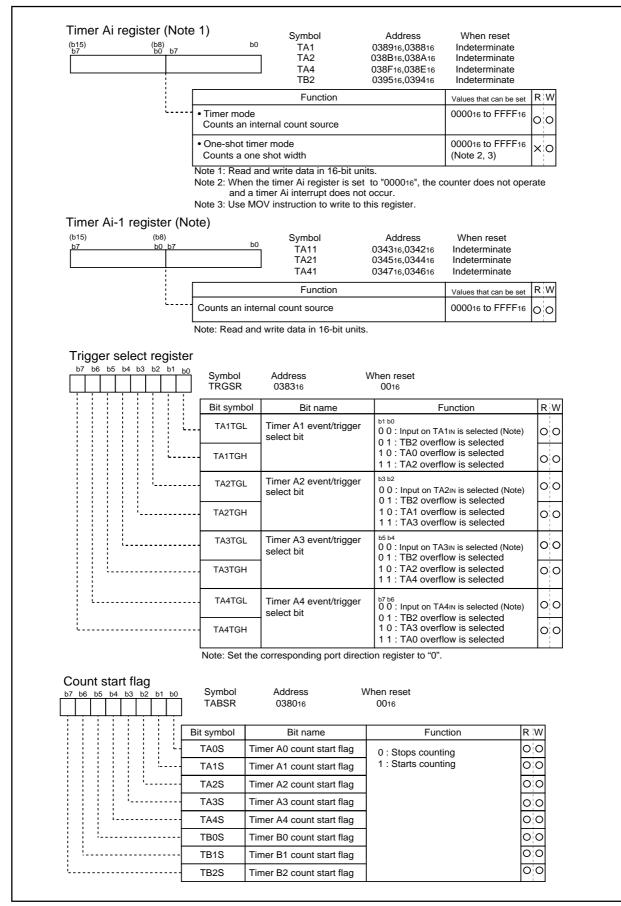

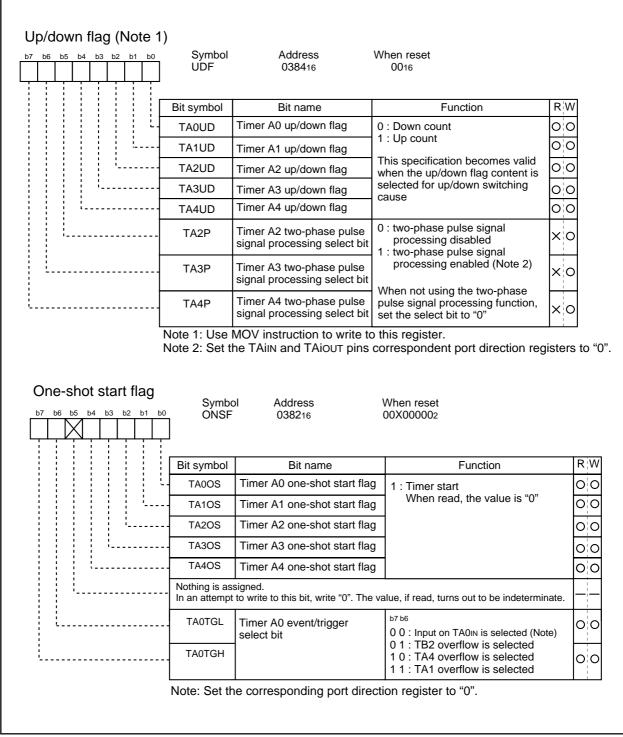

| 038016           | Count start flag (TABSR)                                                                           | 1-81  |

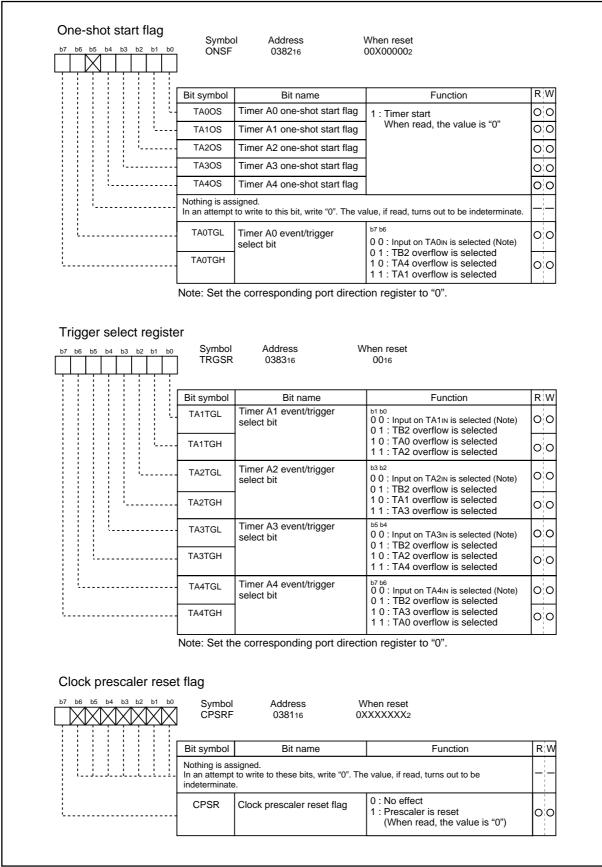

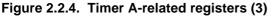

| 038116           | Clock prescaler reset flag (CPSRF)                                                                 |       |

| 038216           | One-shot start flag (ONSF)                                                                         | 1-82  |

| 038316           | Trigger select register (TRGSR)                                                                    |       |

| 038416           | Up-down flag (UDF)                                                                                 | 1-81  |

| 038516           |                                                                                                    |       |

| 038616<br>038716 | Timer A0 register (TA0)                                                                            |       |

| 038816           |                                                                                                    |       |

| 038916           | Timer A1 register (TA1)                                                                            |       |

| 038A16           | Timer A2 register (TA2)                                                                            | 1-81  |

| 038B16           |                                                                                                    | 1-01  |

| 038C16           | Timer A3 register (TA3)                                                                            |       |

| 038D16<br>038E16 |                                                                                                    |       |

| 038E16<br>038F16 | Timer A4 register (TA4)                                                                            |       |

| 039016           |                                                                                                    |       |

| 039116           | Timer B0 register (TB0)                                                                            |       |

| 039216           | Timer B1 register (TB1)                                                                            |       |

| 039316           |                                                                                                    | 1-91  |

| 039416           | Timer B2 register (TB2)                                                                            |       |

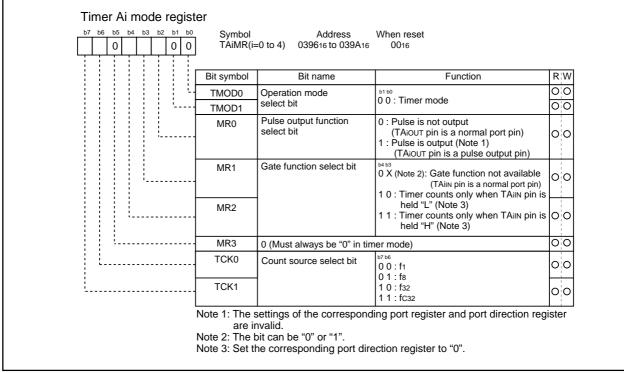

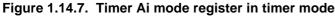

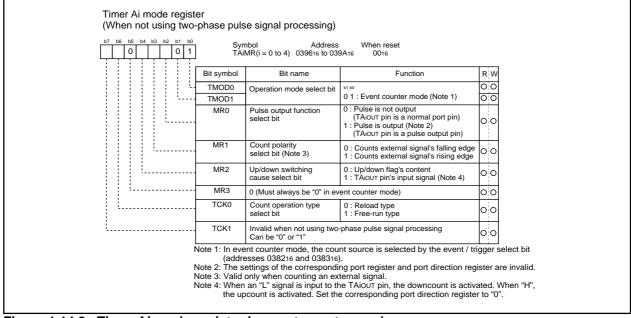

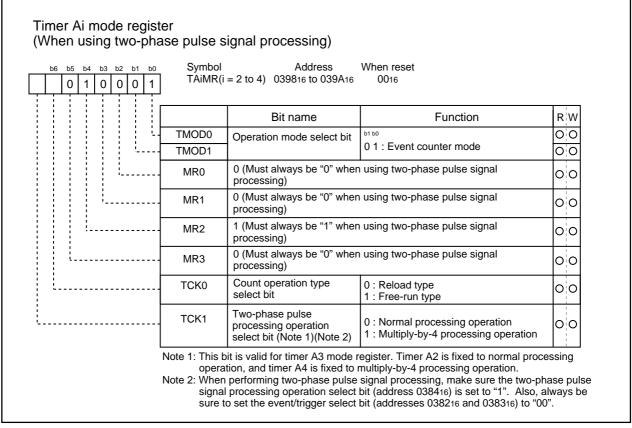

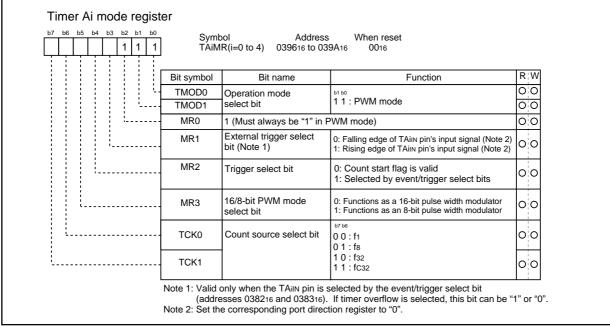

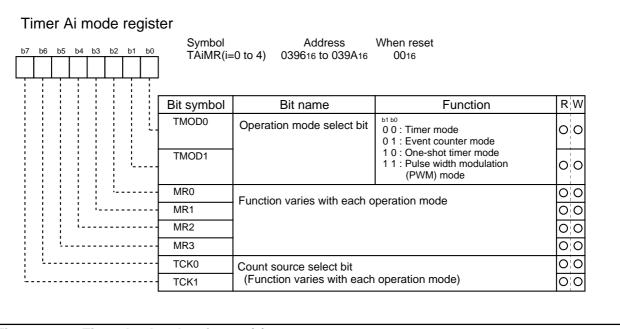

| 039516<br>039616 | Timer A0 mode register (TA0MR)                                                                     |       |

| 039616           | Timer A1 mode register (TA000R)                                                                    |       |

| 039816           | Timer A2 mode register (TA2MR)                                                                     | 1-80  |

| 039916           | Timer A3 mode register (TA3MR)                                                                     | 1.00  |

| 039A16           | Timer A4 mode register (TA4MR)                                                                     |       |

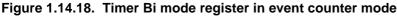

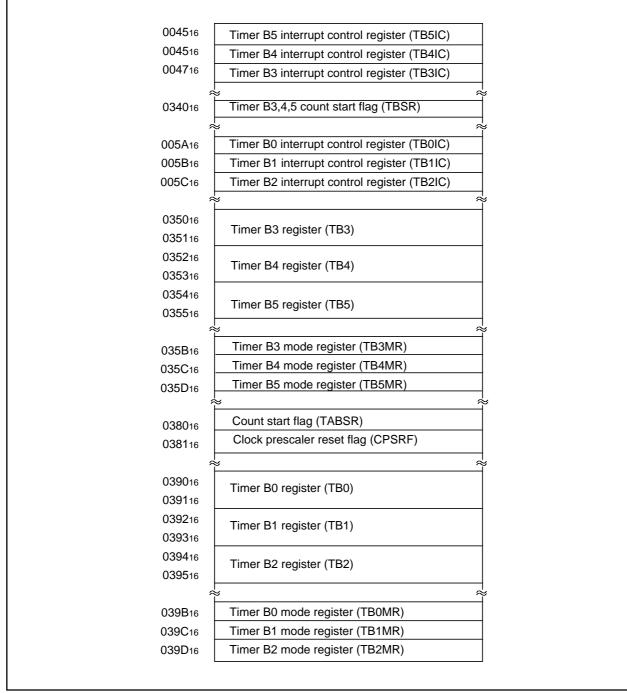

| 039B16           | Timer B0 mode register (TB0MR)                                                                     |       |

| 039C16           | Timer B1 mode register (TB1MR)                                                                     | 1-90  |

| 039D16           | Timer B2 mode register (TB2MR)                                                                     |       |

| 039E16<br>039F16 |                                                                                                    |       |

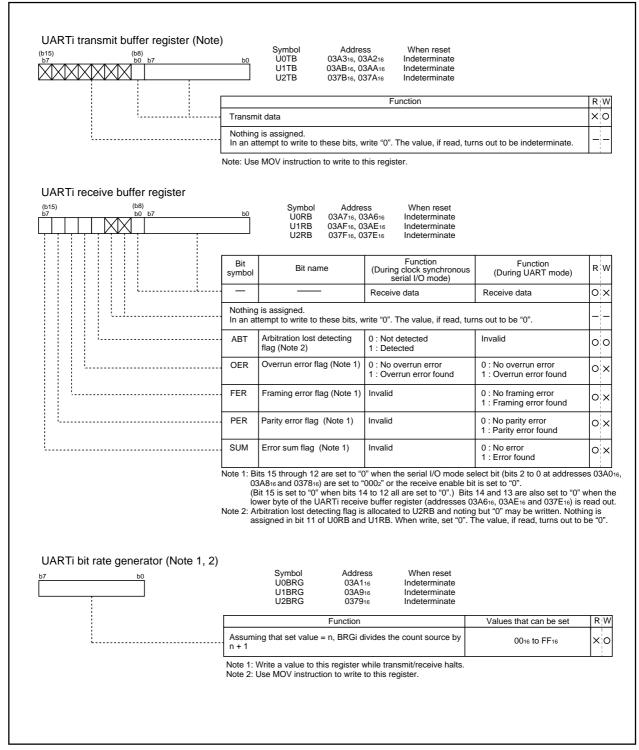

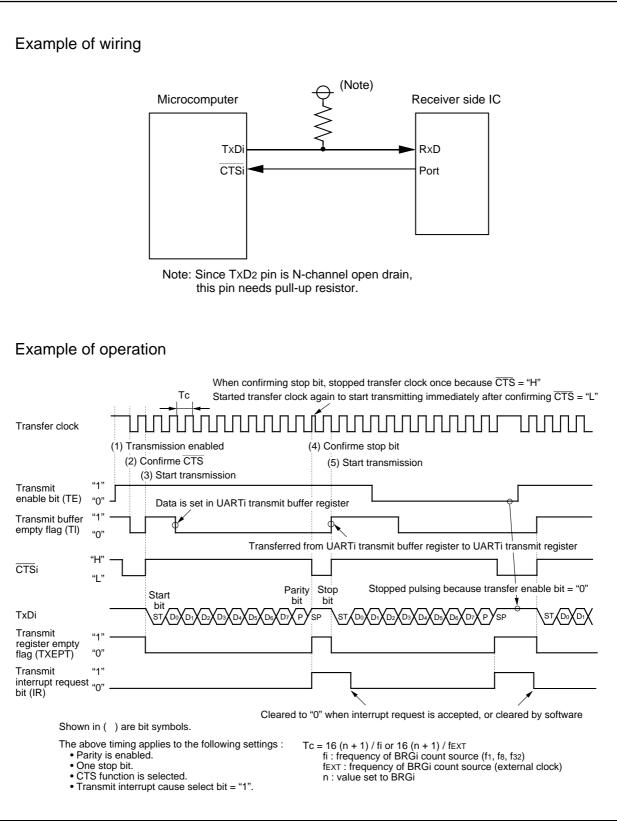

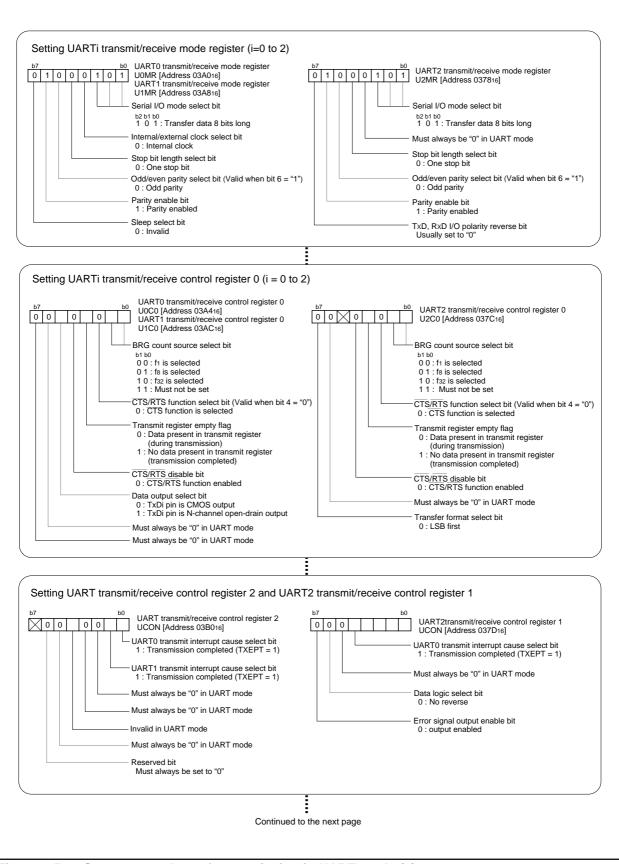

| 03A016           | UART0 transmit/receive mode register (U0MR)                                                        | 1-113 |

| 03A116           | UART0 bit rate generator (U0BRG)                                                                   | 1 110 |

| 03A216           | • · · ·                                                                                            | 1-112 |

| 03A316           | UART0 transmit buffer register (U0TB)                                                              |       |

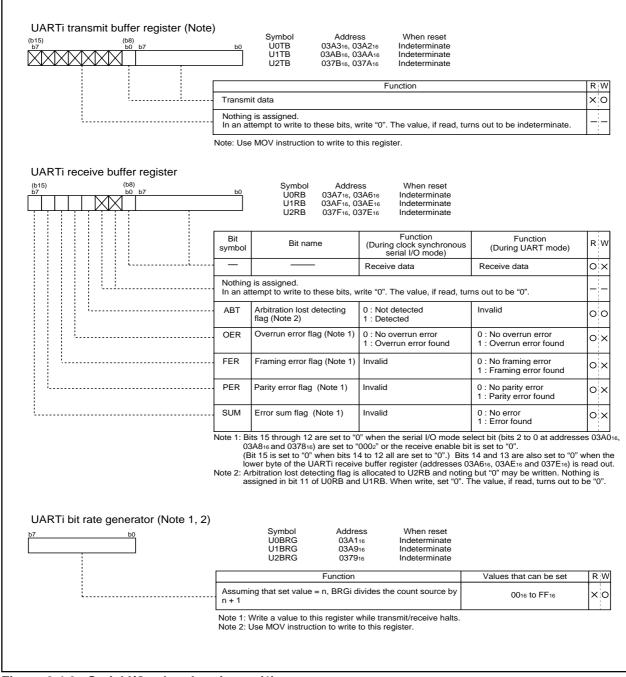

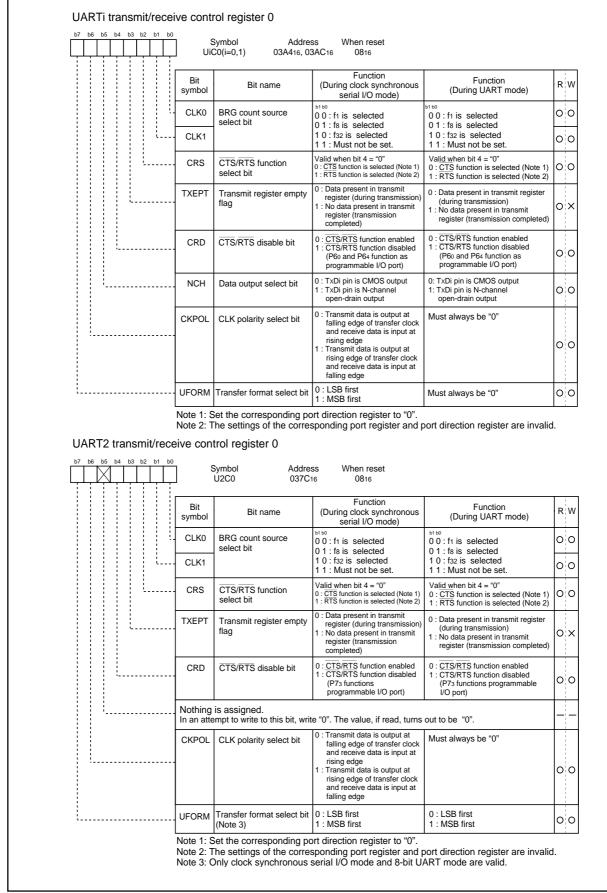

| 03A416           | UART0 transmit/receive control register 0 (U0C0)                                                   | 1-114 |

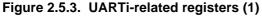

| 03A516           | UART0 transmit/receive control register 1 (U0C1)                                                   | 1-115 |

| 03A616<br>03A716 | UART0 receive buffer register (U0RB)                                                               | 1-112 |

| 03A816           | UART1 transmit/receive mode register (U1MR)                                                        | 1-113 |

| 03A916           | UART1 bit rate generator (U1BRG)                                                                   | 1 110 |

| 03AA16           | LIAPT1 transmit buffer register (LI1TB)                                                            | 1-112 |

| 03AB16           | UART1 transmit buffer register (U1TB)                                                              |       |

| 03AC16           | UART1 transmit/receive control register 0 (U1C0)                                                   | 1-114 |

| 03AD16           | UART1 transmit/receive control register 1 (U1C1)                                                   | 1-115 |

| 03AE16<br>03AF16 | UART1 receive buffer register (U1RB)                                                               | 1-112 |

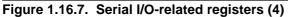

| 03B016           | UART transmit/receive control register 2 (UCON)                                                    | 1-116 |

| 03B116           |                                                                                                    |       |

| 03B216           |                                                                                                    |       |

| 03B316           |                                                                                                    |       |

| 03B416           |                                                                                                    |       |

| 03B516           | Elash momony control register 1 (EMP1) (Note 1)                                                    |       |

| 03B616<br>03B716 | Flash memory control register 1 (FMR1) (Note 1)<br>Flash memory control register 0 (FMR0) (Note 1) | 1-221 |

| 03B716<br>03B816 | DMA0 request cause select register (DM0SL)                                                         | 1-70  |

| 03B916           | ( <b>voz</b> )                                                                                     |       |

| 03BA16           | DMA1 request cause select register (DM1SL)                                                         | 1-71  |

| 03BB16           |                                                                                                    |       |

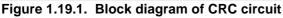

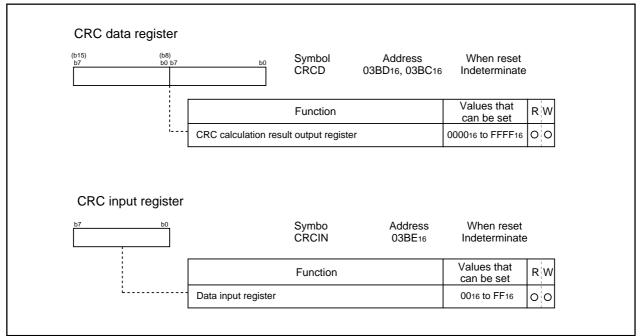

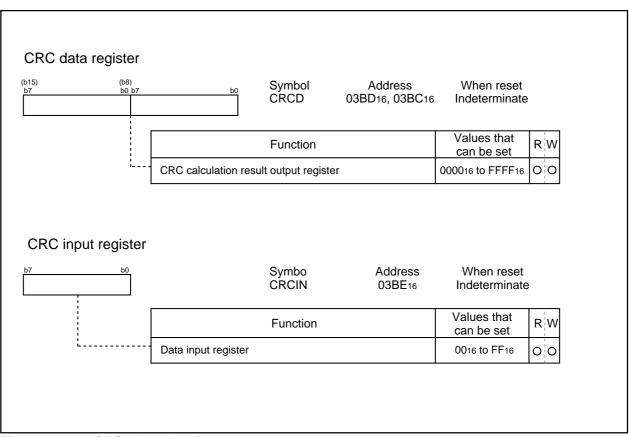

| 03BC16           | CRC data register (CRCD)                                                                           |       |

| 03BD16           | CRC input register (CRCIN)                                                                         | 1-161 |

| 03BE16<br>03BF16 |                                                                                                    |       |

|                  | I                                                                                                  |       |

Note 1 : This register is only exist in flash memory version. Note 2 : Locations in the SFR area where nothing is allocated are reserved areas. Do not access these areas for read or write.

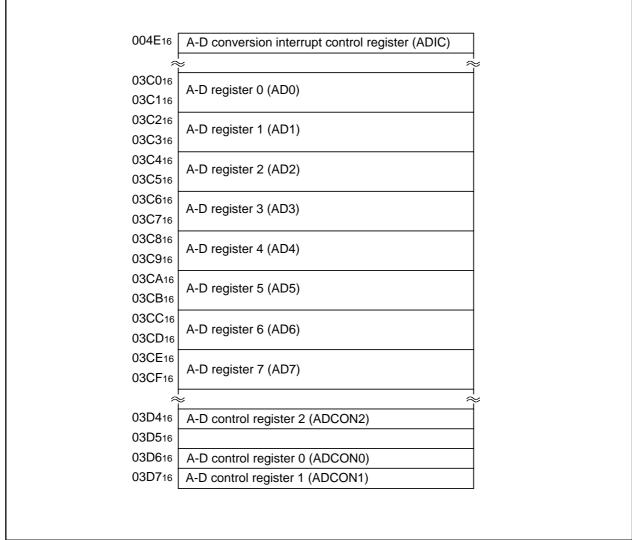

#### Quick Reference to Pages Classified by Address

| Addre            | ss Register                                                                             | Page    |

|------------------|-----------------------------------------------------------------------------------------|---------|

| 03C016<br>03C116 | A-D register 0 (AD0)                                                                    |         |

| 03C216<br>03C316 | A-D register 1 (AD1)                                                                    |         |

| 03C416<br>03C516 | A-D register 2 (AD2)                                                                    |         |

| 03C616<br>03C716 | A-D register 3 (AD3)                                                                    |         |

| 03C816<br>03C916 | A-D register 4 (AD4)                                                                    | 1-152   |

| 03CA16<br>03CB16 | A-D register 5 (AD5)                                                                    |         |

| 03CC16<br>03CD16 | A-D register 6 (AD6)                                                                    |         |

| 03CE16<br>03CF16 | A-D register 7 (AD7)                                                                    |         |

| 03D016<br>03D116 |                                                                                         | _       |

| 03D216<br>03D316 |                                                                                         |         |

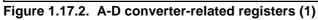

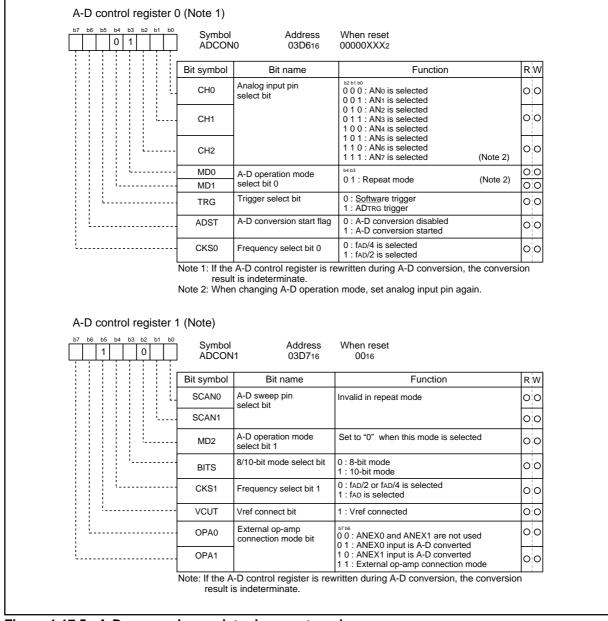

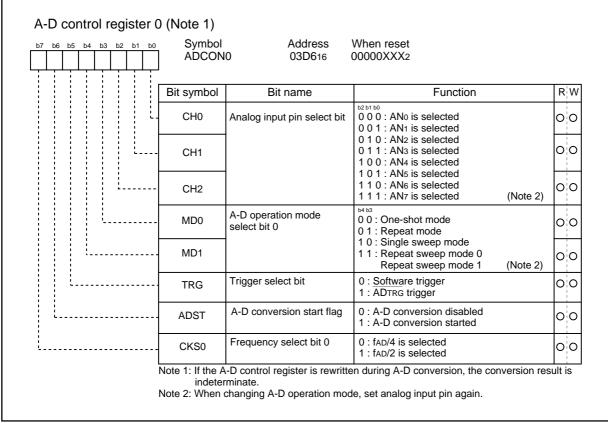

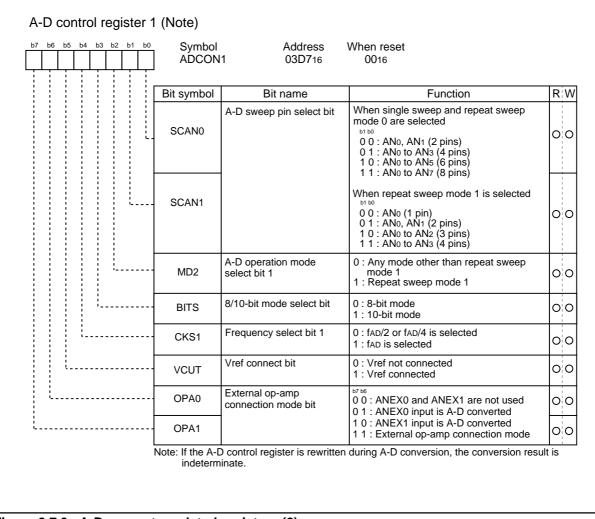

| 03D416<br>03D516 | A-D control register 2 (ADCON2)                                                         | 1-152   |

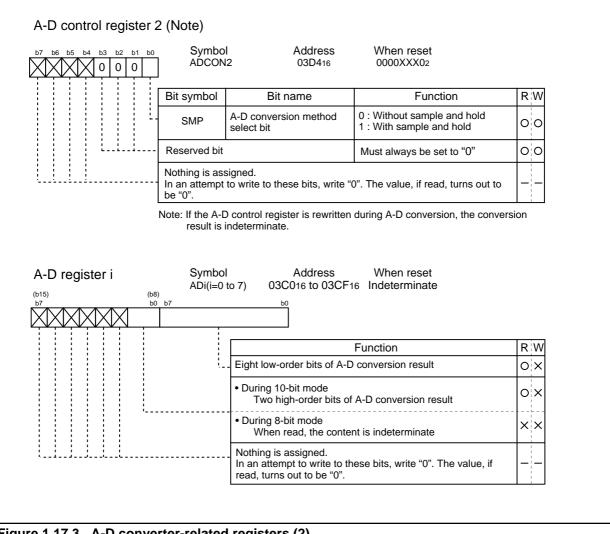

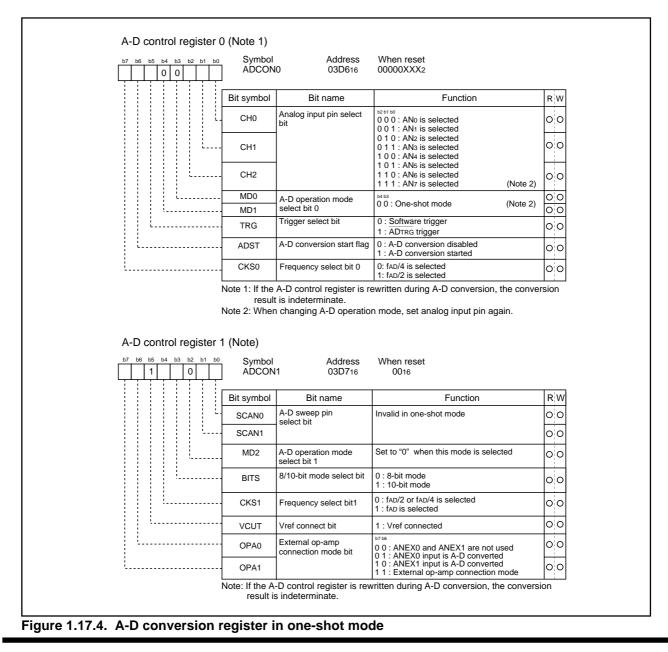

| 03D616<br>03D716 | A-D control register 0 (ADCON0)<br>A-D control register 1 (ADCON1)                      | 1-151   |

| 03D816<br>03D916 | D-A register 0 (DA0)                                                                    | -       |

| 03DA16<br>03DB16 | D-A register 1 (DA1)                                                                    | 1-160   |

| 03DC16<br>03DD16 | D-A control register (DACON)                                                            | -       |

| 03DE16<br>03DF16 |                                                                                         | -       |

| 03E016<br>03E116 | Port P0 register (P0)                                                                   | 1-169   |

| 03E216           | Port P1 register (P1) Port P0 direction register (PD0) Port P1 direction register (PD1) | 1-168   |

| 03E316<br>03E416 | Port P1 direction register (PD1) Port P2 register (P2) Port P2 register (P2)            | 1-169   |

| 03E516<br>03E616 | Port P3 register (P3)<br>Port P2 direction register (PD2)                               | 1-168   |

| 03E716<br>03E816 | Port P3 direction register (PD3) Port P4 register (P4)                                  | 1-169   |

| 03E916<br>03EA16 | Port P5 register (P5)<br>Port P4 direction register (PD4)                               | - 1-168 |

| 03EB16<br>03EC16 | Port P5 direction register (PD5)<br>Port P6 register (P6)                               | 1-169   |

| 03ED16<br>03EE16 | Port P7 register (P7)<br>Port P6 direction register (PD6)                               | - 1-168 |

| 03EF16<br>03F016 | Port P7 direction register (PD7)<br>Port P8 register (P8)                               | 1-169   |

| 03F116<br>03F216 | Port P9 register (P9)<br>Port P8 direction register (PD8)                               |         |

| 03F316<br>03F416 | Port P9 direction register (PD9)<br>Port P10 register (P10)                             | 1-168   |

| 03F516<br>03F616 | Port P10 direction register (PD10)                                                      | 1-168   |

| 03F716<br>03F816 |                                                                                         |         |

| 03F916           |                                                                                         |         |

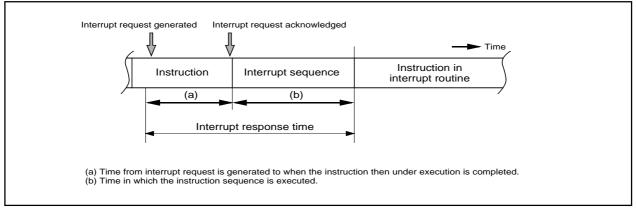

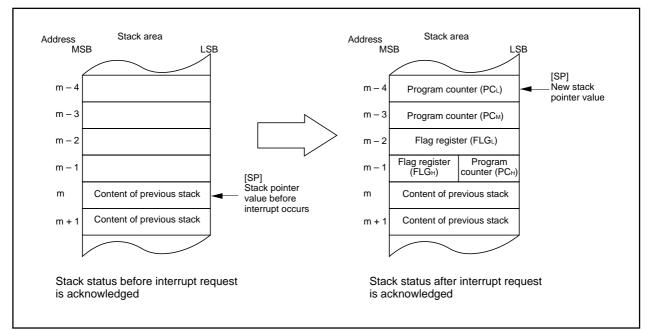

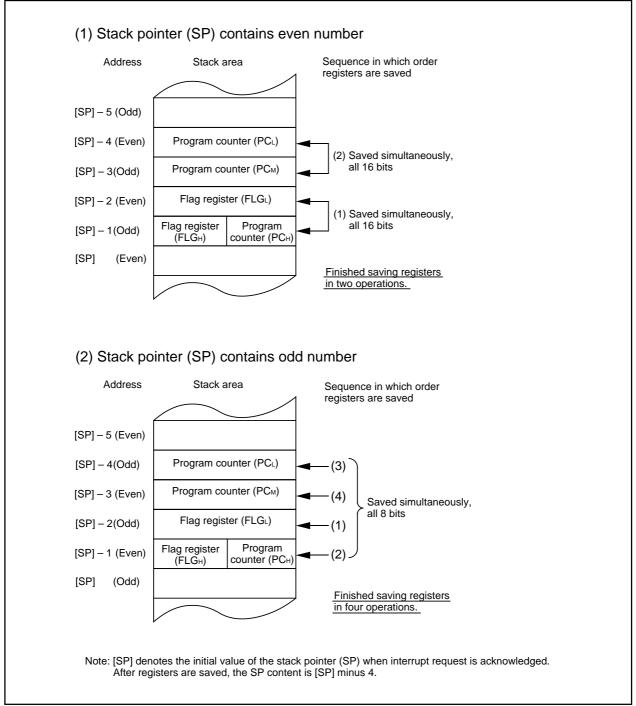

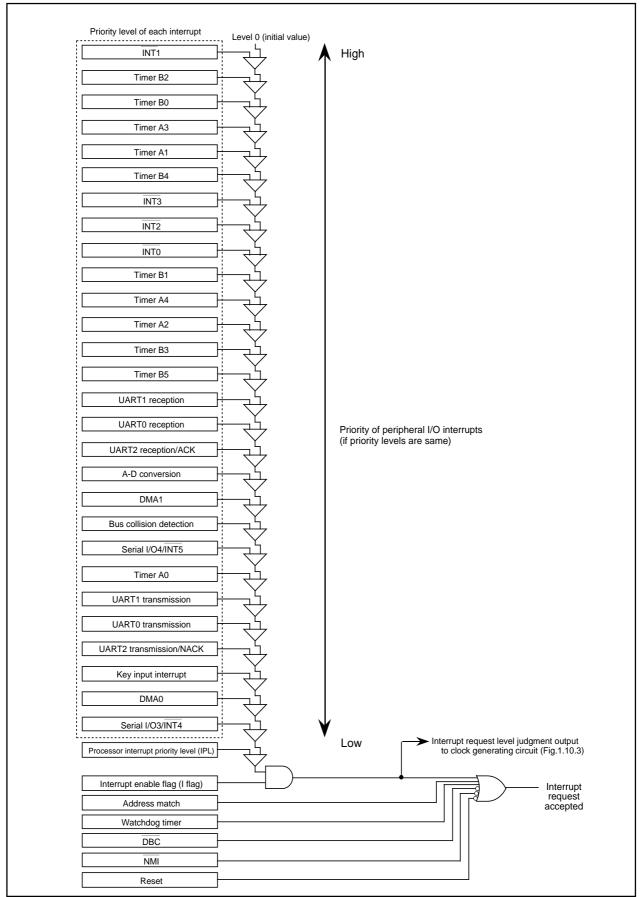

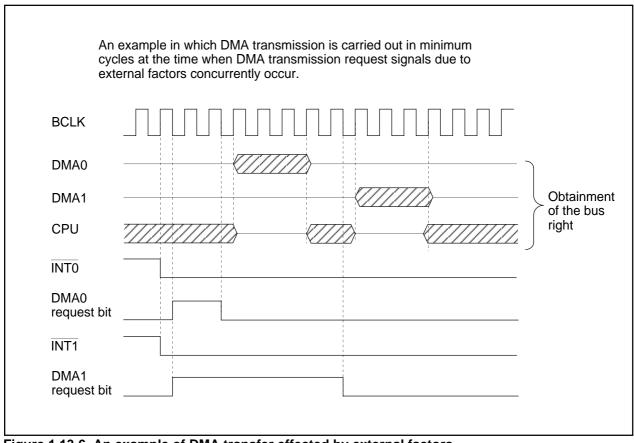

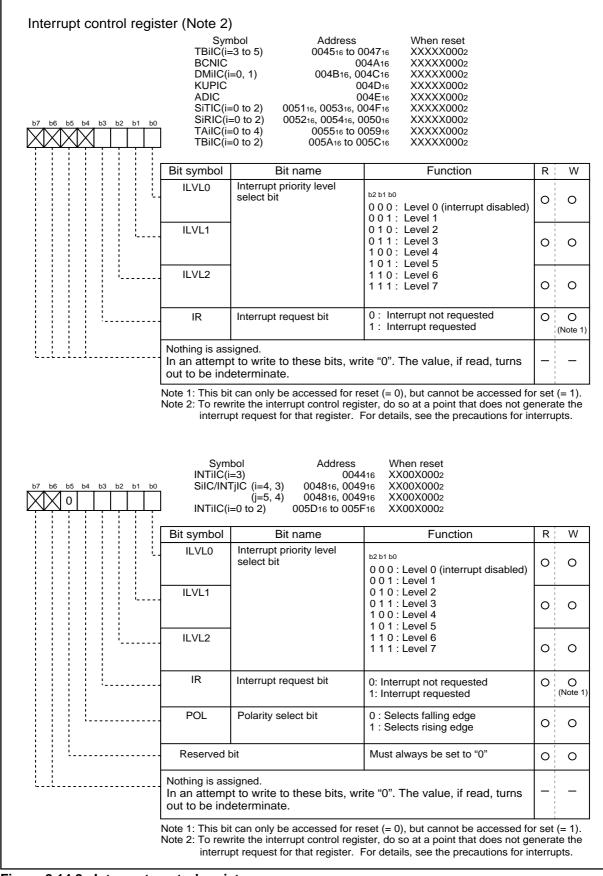

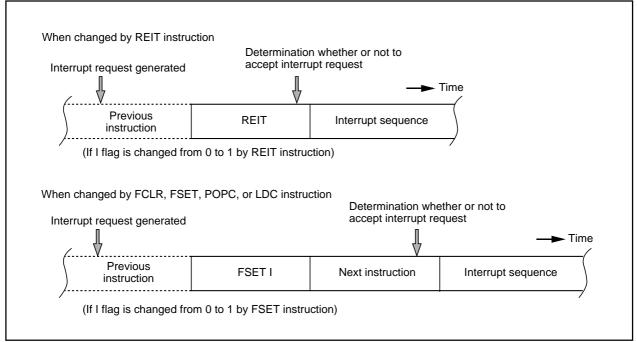

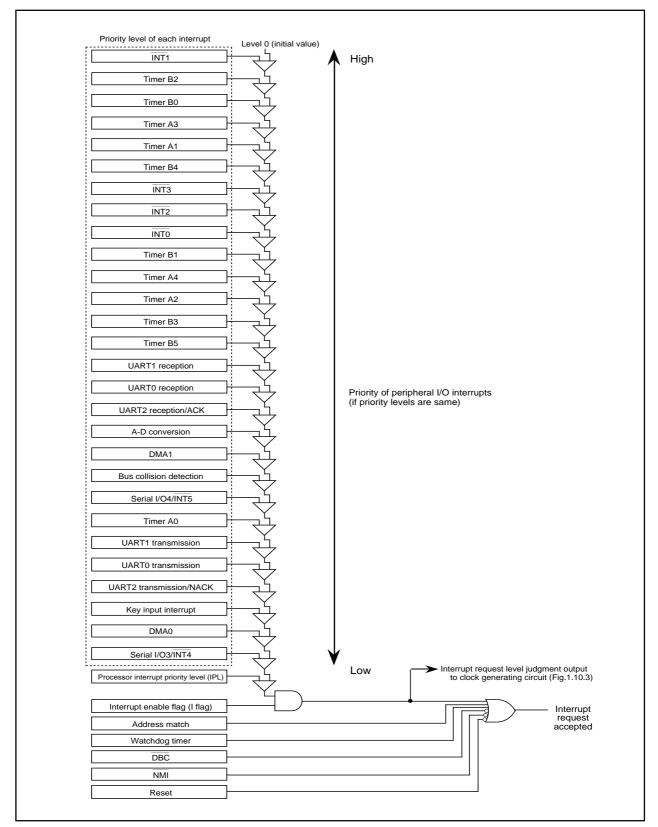

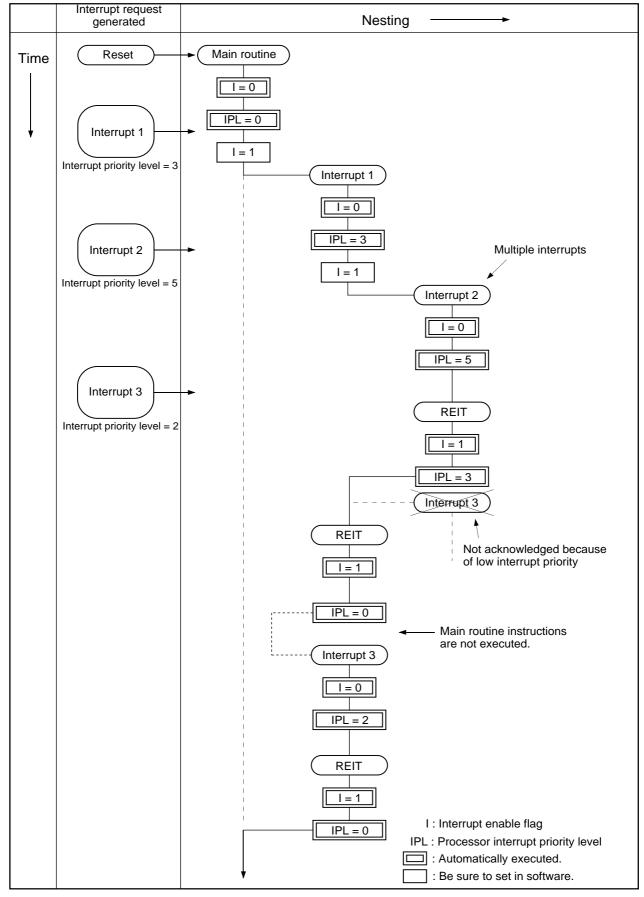

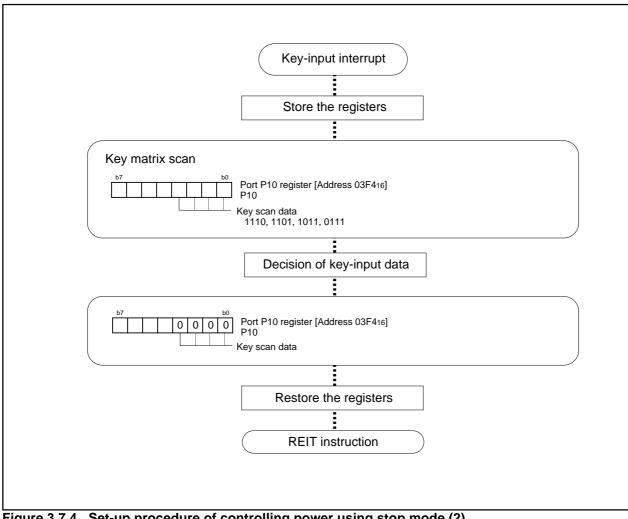

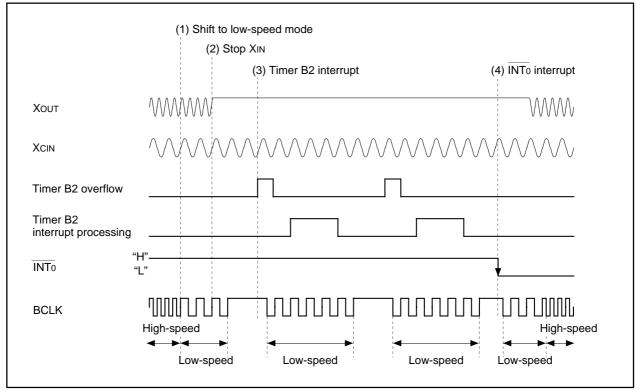

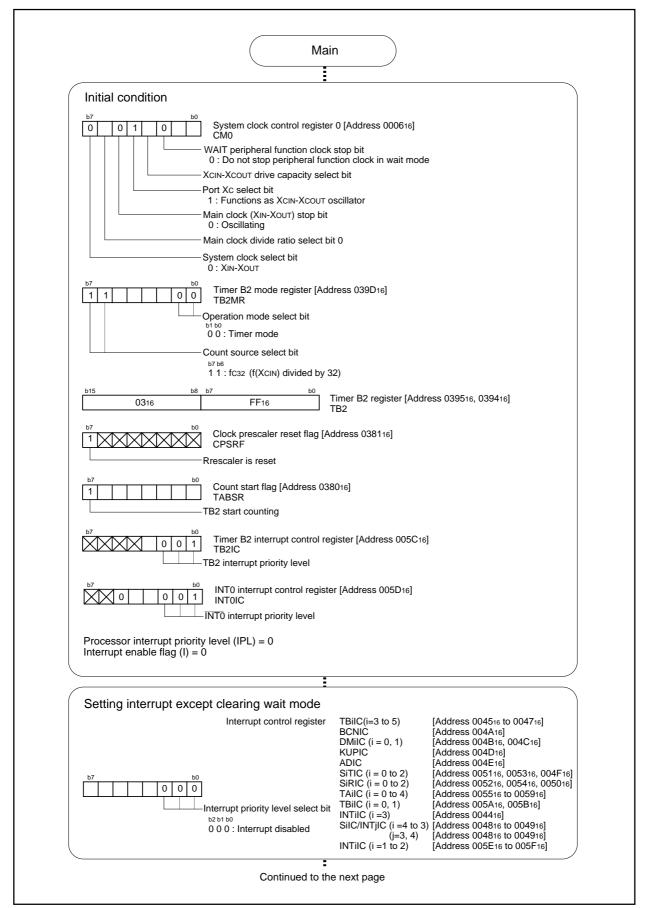

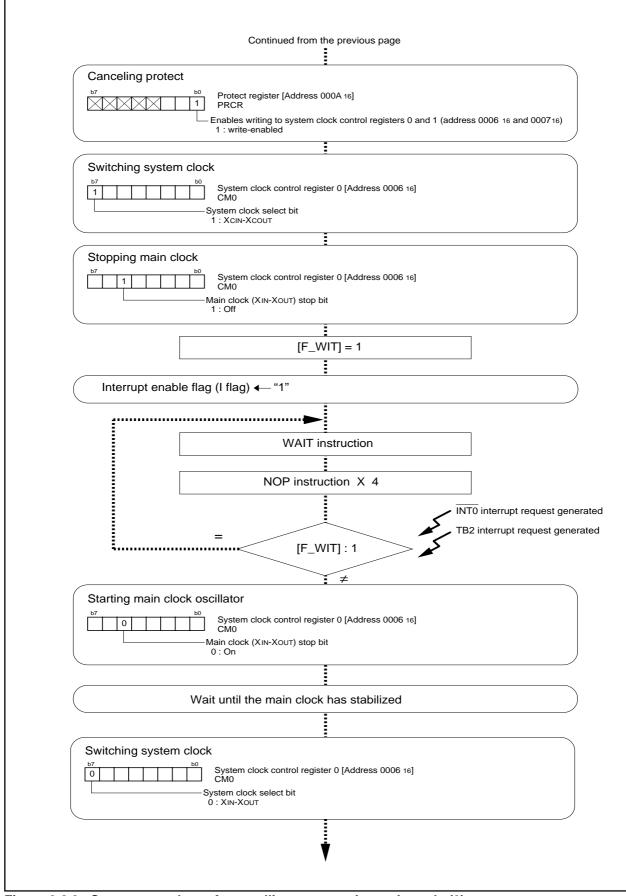

| 03FA16<br>03FB16 |                                                                                         | -       |